Loading...

Searching...

No Matches

arm_cortex_m4.h File Reference

Register definitions and bit position enumerations for the Arm Cortex-M4 core peripherals. More...

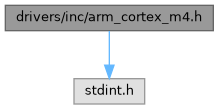

#include <stdint.h>

Include dependency graph for arm_cortex_m4.h:

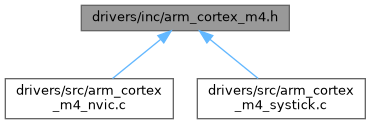

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | NVIC_ISER_REGDEF_ts |

| NVIC Interrupt Set-Enable Registers (NVIC_ISER). More... | |

| struct | NVIC_ICER_REGDEF_ts |

| NVIC Interrupt Clear-Enable Registers (NVIC_ICER). More... | |

| struct | NVIC_ISPR_REGDEF_ts |

| NVIC Interrupt Set-Pending Registers (NVIC_ISPR). More... | |

| struct | NVIC_ICPR_REGDEF_ts |

| NVIC Interrupt Clear-Pending Registers (NVIC_ICPR). More... | |

| struct | NVIC_IABR_REGDEF_ts |

| NVIC Interrupt Active Bit Registers (NVIC_IABR). More... | |

| struct | NVIC_IPR_REGDEF_ts |

| NVIC Interrupt Priority Registers (NVIC_IPR). More... | |

| struct | NVIC_STIR_REGDEF_ts |

| NVIC Software Trigger Interrupt Register (NVIC_STIR). More... | |

| struct | SYST_REGDEF_ts |

| SysTick control and status register block. More... | |

Macros | |

| #define | ADDR_NVIC_ISER (0xE000E100U) |

| #define | ADDR_NVIC_ICER (0xE000E180U) |

| #define | ADDR_NVIC_ISPR (0xE000E200U) |

| #define | ADDR_NVIC_ICPR (0xE000E280U) |

| #define | ADDR_NVIC_IABR (0xE000E300U) |

| #define | ADDR_NVIC_IPR (0xE000E400U) |

| #define | ADDR_NVIC_STIR (0xE000EF00U) |

| #define | ADDR_SYSTICK (0xE000E010U) |

| #define | NVIC_ISER ((NVIC_ISER_REGDEF_ts*)ADDR_NVIC_ISER) |

| #define | NVIC_ICER ((NVIC_ICER_REGDEF_ts*)ADDR_NVIC_ICER) |

| #define | NVIC_ISPR ((NVIC_ISPR_REGDEF_ts*)ADDR_NVIC_ISPR) |

| #define | NVIC_ICPR ((NVIC_ICPR_REGDEF_ts*)ADDR_NVIC_ICPR) |

| #define | NVIC_IABR ((NVIC_IABR_REGDEF_ts*)ADDR_NVIC_IABR) |

| #define | NVIC_IPR ((NVIC_IPR_REGDEF_ts*)ADDR_NVIC_IPR) |

| #define | NVIC_STIR ((NVIC_STIR_REGDEF_ts*)ADDR_NVIC_STIR) |

| #define | SYSTICK ((SYST_REGDEF_ts*)ADDR_SYSTICK) |

Enumerations | |

| enum | SYST_CSR_te { SYST_CSR_ENABLE = 0 , SYST_CSR_TICKINT = 1 , SYST_CSR_CLKSOURCE = 2 , SYST_CSR_COUNTFLAG = 16 } |

| Bit positions within the SysTick Control and Status Register (SYST_CSR). More... | |

| enum | SYST_RVR_te { SYST_RVR_RELOAD = 0 } |

| Bit positions within the SysTick Reload Value Register (SYST_RVR). More... | |

| enum | SYST_CVR_te { SYST_CVR_CURRENT = 0 } |

| Bit positions within the SysTick Current Value Register (SYST_CVR). More... | |

| enum | SYST_CALIB_te { SYST_CALIB_TENMS = 0 , SYST_CALIB_SKEW = 30 , SYST_CALIB_NOREF = 31 } |

| Bit positions within the SysTick Calibration Value Register (SYST_CALIB). More... | |

Detailed Description

Register definitions and bit position enumerations for the Arm Cortex-M4 core peripherals.

This header provides memory-mapped register definitions and bit position enumerations for the following Cortex-M4 core peripherals:

- NVIC (Nested Vectored Interrupt Controller): ISER, ICER, ISPR, ICPR, IABR, IPR, STIR

- SysTick: CSR, RVR, CVR, CALIB

All register structs are accessed via pointer macros cast to their fixed memory-mapped addresses as defined in the ARMv7-M Architecture Reference Manual.

- Version

- 0.1

- Date

- 2026-01-23

- Copyright

- Copyright (c) 2026

Definition in file arm_cortex_m4.h.