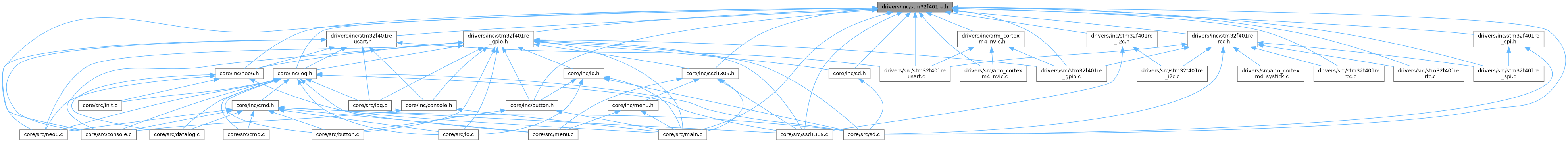

STM32F401RE MCU-specific peripheral register definitions and bit position enumerations.

More...

|

| enum | APB1ENR_te { APB1ENR_PWREN = 28

} |

| | APB1ENR register bit positions (legacy, prefer RCC_APB1ENR_te). More...

|

| enum | PWR_CR_te { PWR_CR_DBP = 8

} |

| | PWR_CR register bit positions. More...

|

| enum | RCC_CR_te { RCC_CR_HSEON = 16

, RCC_CR_HSERDY = 17

} |

| | RCC_CR register bit positions. More...

|

| enum | RCC_BDCR_te {

RCC_BDCR_LSEON = 0

, RCC_BDCR_LSERDY = 1

, RCC_BDCR_LSEBYP = 2

, RCC_BDCR_RTCSEL = 8

,

RCC_BDCR_RTCEN = 15

, RCC_BDCR_BDRST = 16

} |

| | RCC_BDCR register bit positions. More...

|

| enum | RCC_CSR_te { RCC_CSR_LSION = 0

, RCC_CSR_LSIRDY = 1

} |

| | RCC_CSR register bit positions. More...

|

| enum | RTC_CR_te { RTC_CR_FMT = 6

} |

| | RTC_CR register bit positions. More...

|

| enum | RTC_ISR_te { RTC_ISR_RSF = 5

, RTC_ISR_INITF = 6

, RTC_ISR_INIT = 7

} |

| | RTC_ISR register bit positions. More...

|

| enum | RTC_TR_te {

RTC_TR_SU = 0

, RTC_TR_ST = 4

, RTC_TR_MNU = 8

, RTC_TR_MNT = 12

,

RTC_TR_HU = 16

, RTC_TR_HT = 20

, RTC_TR_PM = 22

} |

| | RTC_TR register bit positions (all fields BCD-encoded). More...

|

| enum | RTC_DR_te {

RTC_DR_DU = 0

, RTC_DR_DT = 4

, RTC_DR_MU = 8

, RTC_DR_MT = 12

,

RTC_DR_WDU = 13

, RTC_DR_YU = 16

, RTC_DR_YT = 20

} |

| | RTC_DR register bit positions (all fields BCD-encoded). More...

|

| enum | RTC_PRER_te { RTC_PRER_PREDIV_S = 0

, RTC_PRER_PREDIV_A = 16

} |

| | RTC_PRER register bit positions. More...

|

| enum | SPI_CR1_te {

SPI_CR1_CPHA = 0

, SPI_CR1_CPOL = 1

, SPI_CR1_MSTR = 2

, SPI_CR1_BR = 3

,

SPI_CR1_SPE = 6

, SPI_CR1_LSBFIRST = 7

, SPI_CR1_SSI = 8

, SPI_CR1_SSM = 9

,

SPI_CR1_RXONLY = 10

, SPI_CR1_DFF = 11

, SPI_CR1_CRCNEXT = 12

, SPI_CR1_CRCEN = 13

,

SPI_CR1_BIDIOE = 14

, SPI_CR1_BIDIMODE = 15

} |

| | SPI_CR1 register bit positions. More...

|

| enum | SPI_CR2_te {

SPI_CR2_RXDMAEN = 0

, SPI_CR2_TXDMAEN = 1

, SPI_CR2_SSOE = 2

, SPI_CR2_FRF = 4

,

SPI_CR2_ERRIE = 5

, SPI_CR2_RXNEIE = 6

, SPI_CR2_TXEIE = 7

} |

| | SPI_CR2 register bit positions. More...

|

| enum | SPI_SR_te {

SPI_SR_RXNE = 0

, SPI_SR_TXE = 1

, SPI_SR_CHSIDE = 2

, SPI_SR_UDR = 3

,

SPI_SR_CRCERR = 4

, SPI_SR_MODF = 5

, SPI_SR_OVR = 6

, SPI_SR_BSY = 7

,

SPI_SR_FRE = 8

} |

| | SPI_SR register bit positions. More...

|

| enum | RCC_CFGR_te { RCC_CFGR_SWS = 2

, RCC_CFGR_HPRE = 4

, RCC_CFGR_PPRE1 = 10

, RCC_CFGR_PPRE2 = 13

} |

| | RCC_CFGR register bit positions. More...

|

| enum | I2C_CR1_te {

I2C_CR1_PE = 0

, I2C_CR1_SMBUS = 1

, I2C_CR1_SMBTYPE = 3

, I2C_CR1_ENARP = 4

,

I2C_CR1_ENPEC = 5

, I2C_CR1_ENGC = 6

, I2C_CR1_NOSTRETCH = 7

, I2C_CR1_START = 8

,

I2C_CR1_STOP = 9

, I2C_CR1_ACK = 10

, I2C_CR1_POS = 11

, I2C_CR1_PEC = 12

,

I2C_CR1_ALERT = 13

, I2C_CR1_SWRST = 15

} |

| | I2C_CR1 register bit positions. More...

|

| enum | I2C_CR2_te {

I2C_CR2_FREQ = 0

, I2C_CR2_ITERREN = 8

, I2C_CR2_ITEVTEN = 9

, I2C_CR2_ITBUFEN = 10

,

I2C_CR2_DMAEN = 11

, I2C_CR2_LAST = 12

} |

| | I2C_CR2 register bit positions. More...

|

| enum | I2C_SR1_te {

I2C_SR1_SB = 0

, I2C_SR1_ADDR = 1

, I2C_SR1_BTF = 2

, I2C_SR1_ADD10 = 3

,

I2C_SR1_STOPF = 4

, I2C_SR1_RxNE = 6

, I2C_SR1_TxE = 7

, I2C_SR1_BERR = 8

,

I2C_SR1_ARLO = 9

, I2C_SR1_AF = 10

, I2C_SR1_OVR = 11

, I2C_SR1_PECERR = 12

,

I2C_SR1_TIMEOUT = 14

, I2C_SR1_SMBALERT = 15

} |

| | I2C_SR1 register bit positions. More...

|

| enum | I2C_SR2_te {

I2C_SR2_MSL = 0

, I2C_SR2_BUSY = 1

, I2C_SR2_TRA = 2

, I2C_SR2_GENCALL = 4

,

I2C_SR2_SMBDEFAULT = 5

, I2C_SR2_SMBHOST = 6

, I2C_SR2_DUALF = 7

, I2C_SR2_PEC = 8

} |

| | I2C_SR2 register bit positions. More...

|

| enum | I2C_CCR_te { I2C_CCR_CCR = 0

, I2C_CCR_DUTY = 14

, I2C_CCR_FS = 15

} |

| | I2C_CCR register bit positions. More...

|

| enum | I2C_OAR1_te { I2C_OAR1_ADD0 = 0

, I2C_OAR1_ADD7_1 = 1

, I2C_OAR1_ADD9_8 = 8

, I2C_OAR1_ADDMODE = 15

} |

| | I2C_OAR1 register bit positions. More...

|

| enum | USART_SR_te {

USART_SR_PE = 0

, USART_SR_FE = 1

, USART_SR_NF = 2

, USART_SR_ORE = 3

,

USART_SR_IDLE = 4

, USART_SR_RXNE = 5

, USART_SR_TC = 6

, USART_SR_TXE = 7

,

USART_SR_LBD = 8

, USART_SR_CTS = 9

} |

| | USART_SR register bit positions. More...

|

| enum | USART_BRR_te { USART_BRR_DIV_FRACTION = 0

, USART_BRR_DIV_MANTISSA = 4

} |

| | USART_BRR register bit positions. More...

|

| enum | USART_CR1_te {

USART_CR1_SBK = 0

, USART_CR1_RWU = 1

, USART_CR1_RE = 2

, USART_CR1_TE = 3

,

USART_CR1_IDLEIE = 4

, USART_CR1_RXNEIE = 5

, USART_CR1_TCIE = 6

, USART_CR1_TXEIE = 7

,

USART_CR1_PEIE = 8

, USART_CR1_PS = 9

, USART_CR1_PCE = 10

, USART_CR1_WAKE = 11

,

USART_CR1_M = 12

, USART_CR1_UE = 13

, USART_CR1_OVER8 = 15

} |

| | USART_CR1 register bit positions. More...

|

| enum | USART_CR2_te {

USART_CR2_ADD = 0

, USART_CR2_LBDL = 5

, USART_CR2_LBDIE = 6

, USART_CR2_LBCL = 8

,

USART_CR2_CPHA = 9

, USART_CR2_CPOL = 10

, USART_CR2_CLKEN = 11

, USART_CR2_STOP = 12

,

USART_CR2_LINEN = 14

} |

| | USART_CR2 register bit positions. More...

|

| enum | USART_CR3_te {

USART_CR3_EIE = 0

, USART_CR3_IREN = 1

, USART_CR3_IRLP = 2

, USART_CR3_HDSEL = 3

,

USART_CR3_NACK = 4

, USART_CR3_SCEN = 5

, USART_CR3_DMAR = 6

, USART_CR3_DMAT = 7

,

USART_CR3_RTSE = 8

, USART_CR3_CTSE = 9

, USART_CR3_CTSIE = 10

, USART_CR3_ONEBIT = 11

} |

| | USART_CR3 register bit positions. More...

|

| enum | RCC_AHB1ENR_te {

RCC_AHB1ENR_GPIOAEN = 0

, RCC_AHB1ENR_GPIOBEN = 1

, RCC_AHB1ENR_GPIOCEN = 2

, RCC_AHB1ENR_GPIODEN = 3

,

RCC_AHB1ENR_GPIOEEN = 4

, RCC_AHB1ENR_GPIOHEN = 7

, RCC_AHB1ENR_CRCEN = 12

, RCC_AHB1ENR_DMA1EN = 21

,

RCC_AHB1ENR_DMA2EN = 22

} |

| | RCC_AHB1ENR register bit positions. More...

|

| enum | RCC_AHB1RSTR_te {

RCC_AHB1RSTR_GPIOARST = 0

, RCC_AHB1RSTR_GPIOBRST = 1

, RCC_AHB1RSTR_GPIOCRST = 2

, RCC_AHB1RSTR_GPIODRST = 3

,

RCC_AHB1RSTR_GPIOERST = 4

, RCC_AHB1RSTR_GPIOHRST = 7

, RCC_AHB1RSTR_CRCRST = 12

, RCC_AHB1RSTR_DMA1RST = 21

,

RCC_AHB1RSTR_DMA2RST = 22

} |

| | RCC_AHB1RSTR register bit positions. More...

|

| enum | RCC_APB1ENR_te {

RCC_APB1ENR_TIM2EN = 0

, RCC_APB1ENR_TIM3EN = 1

, RCC_APB1ENR_TIM4EN = 2

, RCC_APB1ENR_TIM5EN = 3

,

RCC_APB1ENR_WWDGEN = 11

, RCC_APB1ENR_SPI2EN = 14

, RCC_APB1ENR_SPI3EN = 15

, RCC_APB1ENR_USART2EN = 17

,

RCC_APB1ENR_I2C1EN = 21

, RCC_APB1ENR_I2C2EN = 22

, RCC_APB1ENR_I2C3EN = 23

, RCC_APB1ENR_PWREN = 28

} |

| | RCC_APB1ENR register bit positions. More...

|

| enum | RCC_APB1RSTR_te {

RCC_APB1RSTR_TIM2RST = 0

, RCC_APB1RSTR_TIM3RST = 1

, RCC_APB1RSTR_TIM4RST = 2

, RCC_APB1RSTR_TIM5RST = 3

,

RCC_APB1RSTR_WWDGRST = 11

, RCC_APB1RSTR_SPI2RST = 14

, RCC_APB1RSTR_SPI3RST = 15

, RCC_APB1RSTR_USART2RST = 17

,

RCC_APB1RSTR_I2C1RST = 21

, RCC_APB1RSTR_I2C2RST = 22

, RCC_APB1RSTR_I2C3RST = 23

, RCC_APB1RSTR_PWRRST = 28

} |

| | RCC_APB1RSTR register bit positions. More...

|

| enum | RCC_APB2ENR_te {

RCC_APB2ENR_TIM1EN = 0

, RCC_APB2ENR_USART1EN = 4

, RCC_APB2ENR_USART6EN = 5

, RCC_APB2ENR_ADC1EN = 8

,

RCC_APB2ENR_SDIOEN = 11

, RCC_APB2ENR_SPI1EN = 12

, RCC_APB2ENR_SPI4EN = 13

, RCC_APB2ENR_SYSCFGEN = 14

,

RCC_APB2ENR_TIM9EN = 16

, RCC_APB2ENR_TIM10EN = 17

, RCC_APB2ENR_TIM11EN = 18

} |

| | RCC_APB2ENR register bit positions. More...

|

| enum | RCC_APB2RSTR_te {

RCC_APB2RSTR_TIM1RST = 0

, RCC_APB2RSTR_USART1RST = 4

, RCC_APB2RSTR_USART6RST = 5

, RCC_APB2RSTR_ADC1RST = 8

,

RCC_APB2RSTR_SDIORST = 11

, RCC_APB2RSTR_SPI1RST = 12

, RCC_APB2RSTR_SPI4RST = 13

, RCC_APB2RSTR_SYSCFGRST = 14

,

RCC_APB2RSTR_TIM9RST = 16

, RCC_APB2RSTR_TIM10RST = 17

, RCC_APB2RSTR_TIM11RST = 18

} |

| | RCC_APB2RSTR register bit positions. More...

|

| enum | IRQn_te {

WWDG_IRQn = 0

, EXTI16_IRQn = 1

, EXTI21_IRQn = 2

, EXTI22_IRQn = 3

,

FLASH_IRQn = 4

, RCC_IRQn = 5

, EXTI0_IRQn = 6

, EXTI1_IRQn = 7

,

EXTI2_IRQn = 8

, EXTI3_IRQn = 9

, EXTI4_IRQn = 10

, DMA1_Stream0_IRQn = 11

,

DMA1_Stream1_IRQn = 12

, DMA1_Stream2_IRQn = 13

, DMA1_Stream3_IRQn = 14

, DMA1_Stream4_IRQn = 15

,

DMA1_Stream5_IRQn = 16

, DMA1_Stream6_IRQn = 17

, ADC_IRQn = 18

, EXTI9_5_IRQn = 23

,

TIM1_BRK_TIM9_IRQn = 24

, TIM1_UP_TIM10_IRQn = 25

, TIM1_TRG_COM_TIM11_IRQn = 26

, TIM1_CC_IRQn = 27

,

TIM2_IRQn = 28

, TIM3_IRQn = 29

, TIM4_IRQn = 30

, I2C1_EV_IRQn = 31

,

I2C1_ER_IRQn = 32

, I2C2_EV_IRQn = 33

, I2C2_ER_IRQn = 34

, SPI1_IRQn = 35

,

SPI2_IRQn = 36

, USART1_IRQn = 37

, USART2_IRQn = 38

, EXTI15_10_IRQn = 40

,

EXTI17_IRQn = 41

, EXTI18_IRQn = 42

, DMA1_Stream7_IRQn = 47

, SDIO_IRQn = 49

,

TIM5_IRQn = 50

, SPI3_IRQn = 51

, DMA2_Stream0_IRQn = 56

, DMA2_Stream1_IRQn = 57

,

DMA2_Stream2_IRQn = 58

, DMA2_Stream3_IRQn = 59

, DMA2_Stream4_IRQn = 60

, OTG_FS_IRQn = 67

,

DMA2_Stream5_IRQn = 68

, DMA2_Stream6_IRQn = 69

, DMA2_Stream7_IRQn = 70

, USART6_IRQn = 71

,

I2C3_EV_IRQn = 72

, I2C3_ER_IRQn = 73

, FPU_IRQn = 81

, SPI4_IRQn = 84

} |

| | IRQ numbers in the STM32F401RE Cortex-M4 vector table. More...

|

| enum | EXTI_LINES_te {

EXTI_LINE_0

, EXTI_LINE_1

, EXTI_LINE_2

, EXTI_LINE_3

,

EXTI_LINE_4

, EXTI_LINE_5

, EXTI_LINE_6

, EXTI_LINE_7

,

EXTI_LINE_8

, EXTI_LINE_9

, EXTI_LINE_10

, EXTI_LINE_11

,

EXTI_LINE_12

, EXTI_LINE_13

, EXTI_LINE_14

, EXTI_LINE_15

,

EXTI_LINE_16

, EXTI_LINE_17

, EXTI_LINE_18

, EXTI_LINE_21 = 21

,

EXTI_LINE_22

} |

| | EXTI line numbers. More...

|

| enum | PORT_CODES_ts {

PA = 0

, PB = 1

, PC = 2

, PD = 3

,

PE = 4

, PH = 7

} |

| | SYSCFG port codes for EXTICRx routing. More...

|

STM32F401RE MCU-specific peripheral register definitions and bit position enumerations.

- Author

- github.com/Baksi675

This header is the central hardware abstraction layer for the STM32F401RE. It provides:

- Peripheral base addresses for APB1, APB2, AHB1, and AHB2 buses

- Register struct definitions for GPIO, RCC, EXTI, SYSCFG, RTC, PWR, SPI, I2C, and USART peripherals, cast via accessor macros (e.g. RCC, GPIOA)

- Bit position enumerations for every configured register, used with the shift-and-mask pattern throughout the driver layer

- IRQ number enumeration (IRQn_te) for use with the NVIC driver

- EXTI line enumeration (EXTI_LINES_te) and SYSCFG port codes (PORT_CODES_ts) for interrupt routing

- Legacy clock enable/disable macros (GPIOx_CLK_EN / GPIOx_CLK_DIS) superseded by rcc_set_pclk_ahb1

- Version

- 0.1

- Date

- 2026-01-22

- Copyright

- Copyright (c) 2026

Definition in file stm32f401re.h.