Public functions to interact with the RCC peripheral. More...

Functions | |

| uint32_t | rcc_get_sysclk (void) |

| Returns the current system clock frequency in Hz. | |

| uint32_t | rcc_get_ahb_clk (void) |

| Returns the current AHB bus clock frequency in Hz. | |

| uint32_t | rcc_get_apb1_clk (void) |

| Returns the current APB1 (low-speed) peripheral bus clock frequency in Hz. | |

| uint32_t | rcc_get_apb2_clk (void) |

| Returns the current APB2 (high-speed) peripheral bus clock frequency in Hz. | |

| void | rcc_set_pclk_ahb1 (RCC_AHB1ENR_te periph_position, EN_STATUS_te en_status) |

| Enables or disables the peripheral clock for an AHB1 peripheral. | |

| void | rcc_set_pclk_apb1 (RCC_APB1ENR_te periph_position, EN_STATUS_te en_status) |

| Enables or disables the peripheral clock for an APB1 peripheral. | |

| void | rcc_set_pclk_apb2 (RCC_APB2ENR_te periph_position, EN_STATUS_te en_status) |

| Enables or disables the peripheral clock for an APB2 peripheral. | |

| void | rcc_reset_periph_ahb1 (RCC_AHB1RSTR_te periph_position) |

| Resets an AHB1 peripheral via RCC_AHB1RSTR. | |

| void | rcc_reset_periph_apb1 (RCC_APB1RSTR_te periph_position) |

| Resets an APB1 peripheral via RCC_APB1RSTR. | |

| void | rcc_reset_periph_apb2 (RCC_APB2RSTR_te periph_position) |

| Resets an APB2 peripheral via RCC_APB2RSTR. | |

| void | rcc_reset_bkpd (void) |

| Resets the backup domain (RTC, backup registers, backup SRAM). | |

Detailed Description

Public functions to interact with the RCC peripheral.

Function Documentation

◆ rcc_get_sysclk()

| uint32_t rcc_get_sysclk | ( | void | ) |

Returns the current system clock frequency in Hz.

Reads the SWS (system clock switch status) field in RCC_CFGR to determine the active clock source:

- SWS = 0: HSI (16 MHz)

- SWS = 1: HSE (8 MHz)

- SWS = 2: PLL (not yet implemented, returns 0)

- Returns

- System clock frequency in Hz, or 0 if the source is unrecognized.

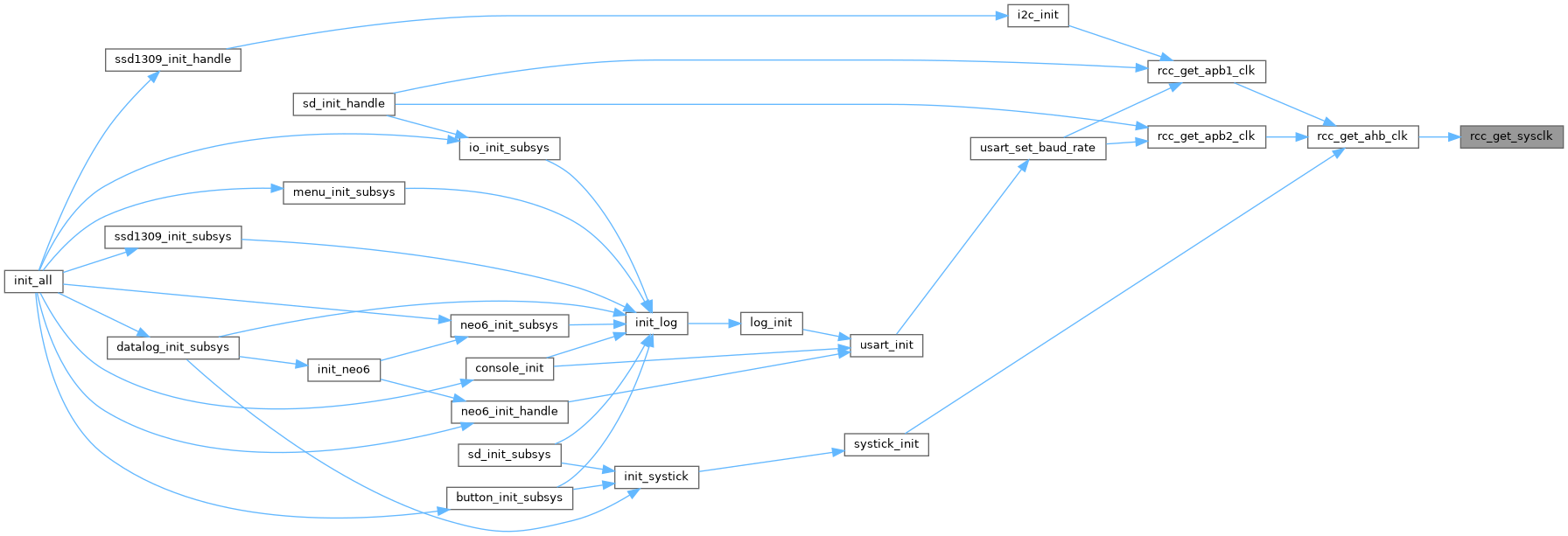

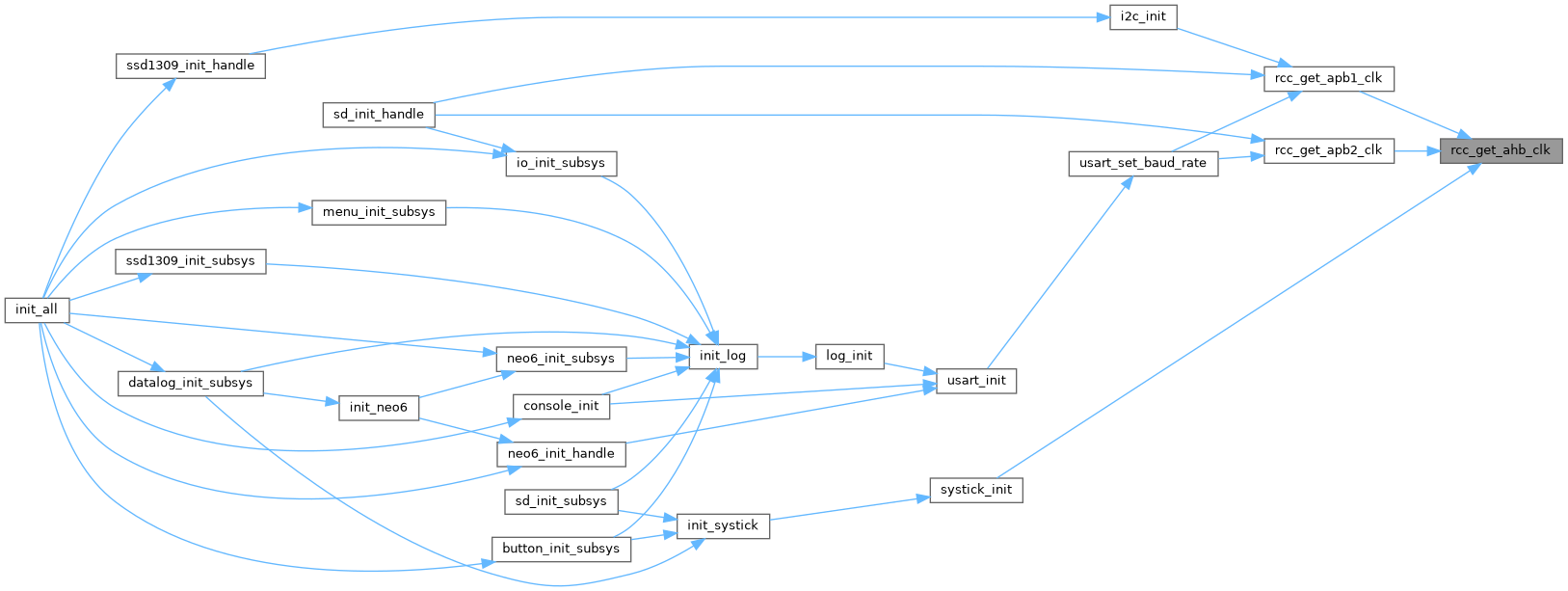

- See also

- rcc_get_sysclk

Definition at line 21 of file stm32f401re_rcc.c.

◆ rcc_get_ahb_clk()

| uint32_t rcc_get_ahb_clk | ( | void | ) |

Returns the current AHB bus clock frequency in Hz.

Reads the HPRE prescaler field from RCC_CFGR and divides the system clock accordingly. The prescaler values map as follows:

- HPRE ≤ 7: divide by 1 (no prescaling)

- HPRE 8–11: divide by 2, 4, 8, 16

- HPRE 12–15: divide by 64, 128, 256, 512

- Returns

- AHB clock frequency in Hz.

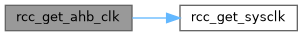

- See also

- rcc_get_ahb_clk

Definition at line 36 of file stm32f401re_rcc.c.

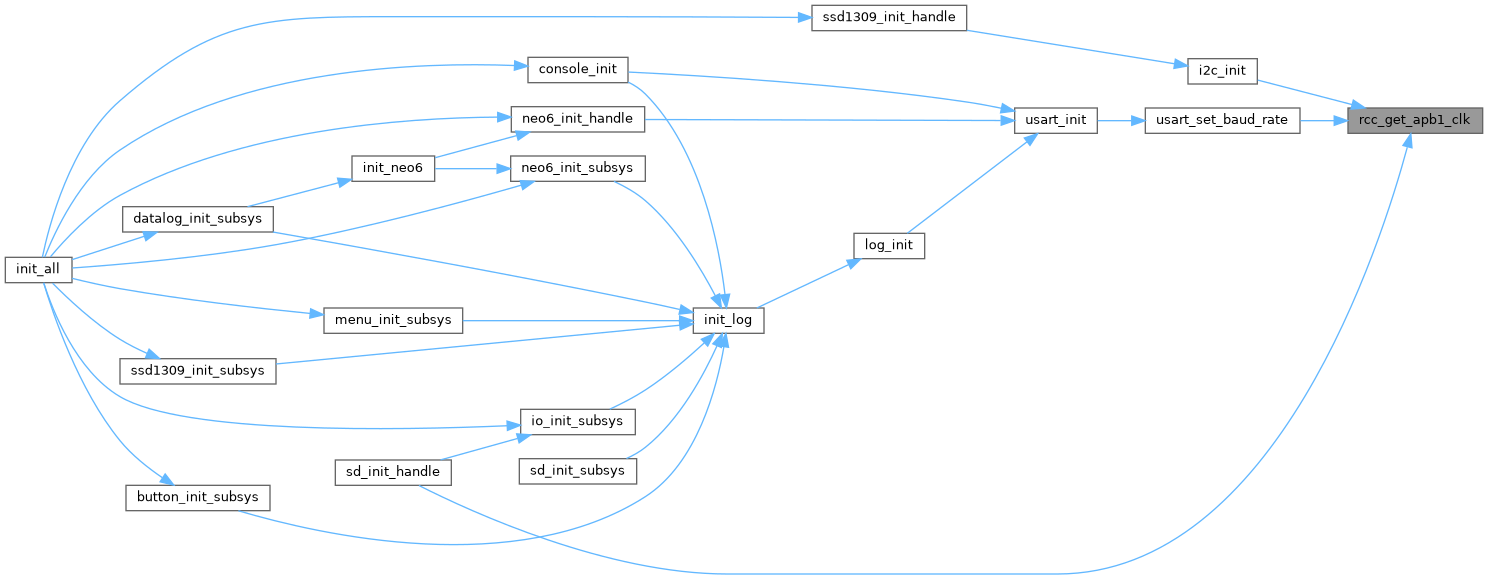

◆ rcc_get_apb1_clk()

| uint32_t rcc_get_apb1_clk | ( | void | ) |

Returns the current APB1 (low-speed) peripheral bus clock frequency in Hz.

Reads the PPRE1 prescaler field from RCC_CFGR and divides the AHB clock accordingly. PPRE1 < 4 maps to no prescaling; PPRE1 ≥ 4 maps to divide by 2^(PPRE1 - 3).

- Returns

- APB1 clock frequency in Hz.

Returns the current APB1 (low-speed) peripheral bus clock frequency in Hz.

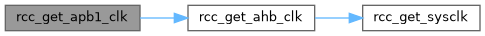

- See also

- rcc_get_apb1_clk

Definition at line 55 of file stm32f401re_rcc.c.

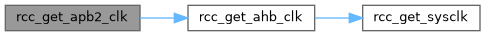

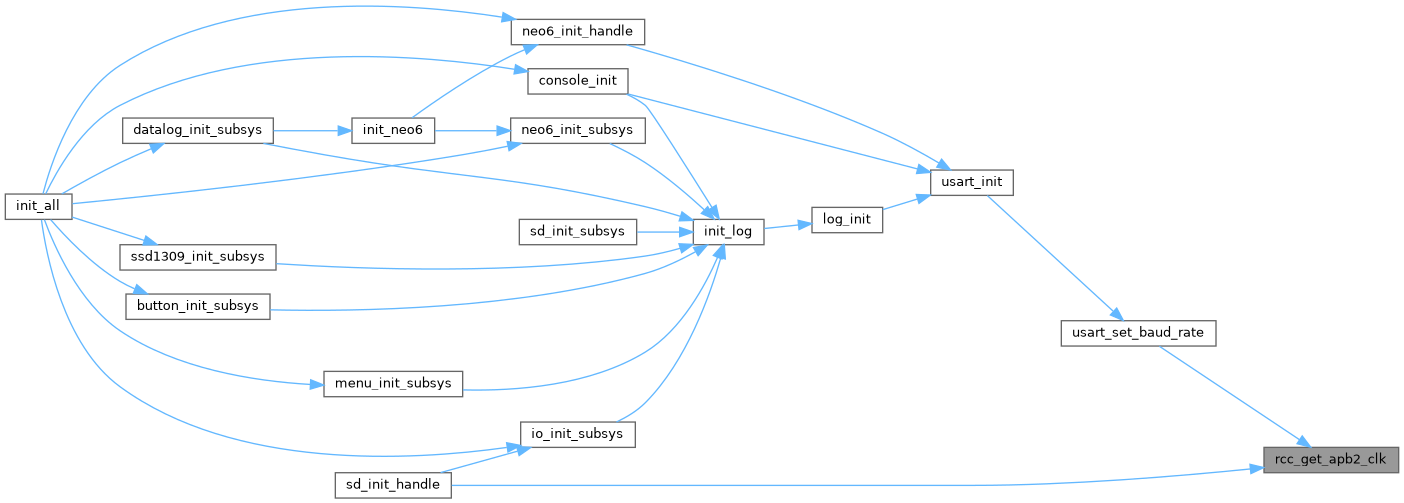

◆ rcc_get_apb2_clk()

| uint32_t rcc_get_apb2_clk | ( | void | ) |

Returns the current APB2 (high-speed) peripheral bus clock frequency in Hz.

Reads the PPRE2 prescaler field from RCC_CFGR and divides the AHB clock accordingly. Same mapping as rcc_get_apb1_clk but using PPRE2.

- Returns

- APB2 clock frequency in Hz.

Returns the current APB2 (high-speed) peripheral bus clock frequency in Hz.

- See also

- rcc_get_apb2_clk

Definition at line 71 of file stm32f401re_rcc.c.

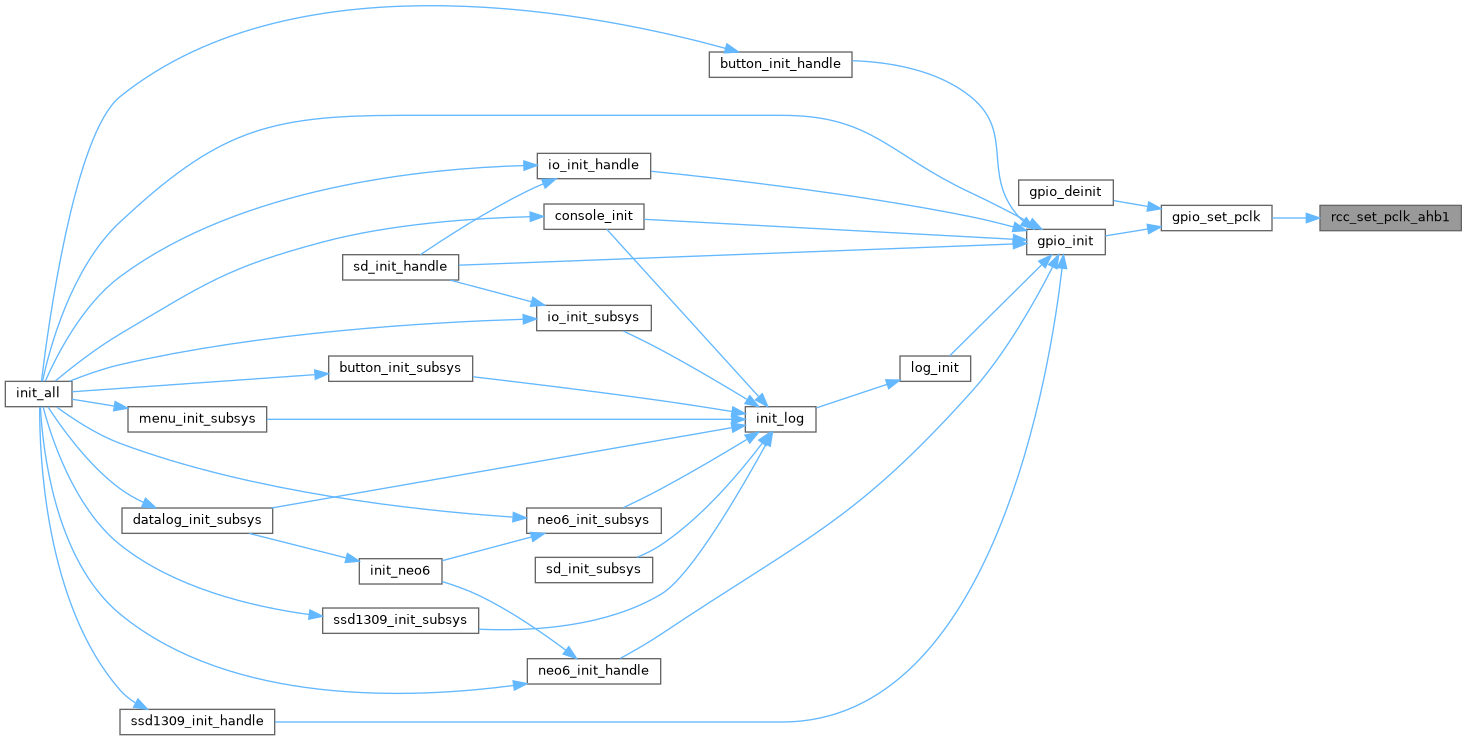

◆ rcc_set_pclk_ahb1()

| void rcc_set_pclk_ahb1 | ( | RCC_AHB1ENR_te | periph_position, |

| EN_STATUS_te | en_status ) |

Enables or disables the peripheral clock for an AHB1 peripheral.

- Parameters

-

[in] periph_position Bit position in RCC_AHB1ENR for the target peripheral. [in] en_status ENABLE to enable the clock, DISABLE to disable it.

- See also

- rcc_set_pclk_ahb1

Definition at line 87 of file stm32f401re_rcc.c.

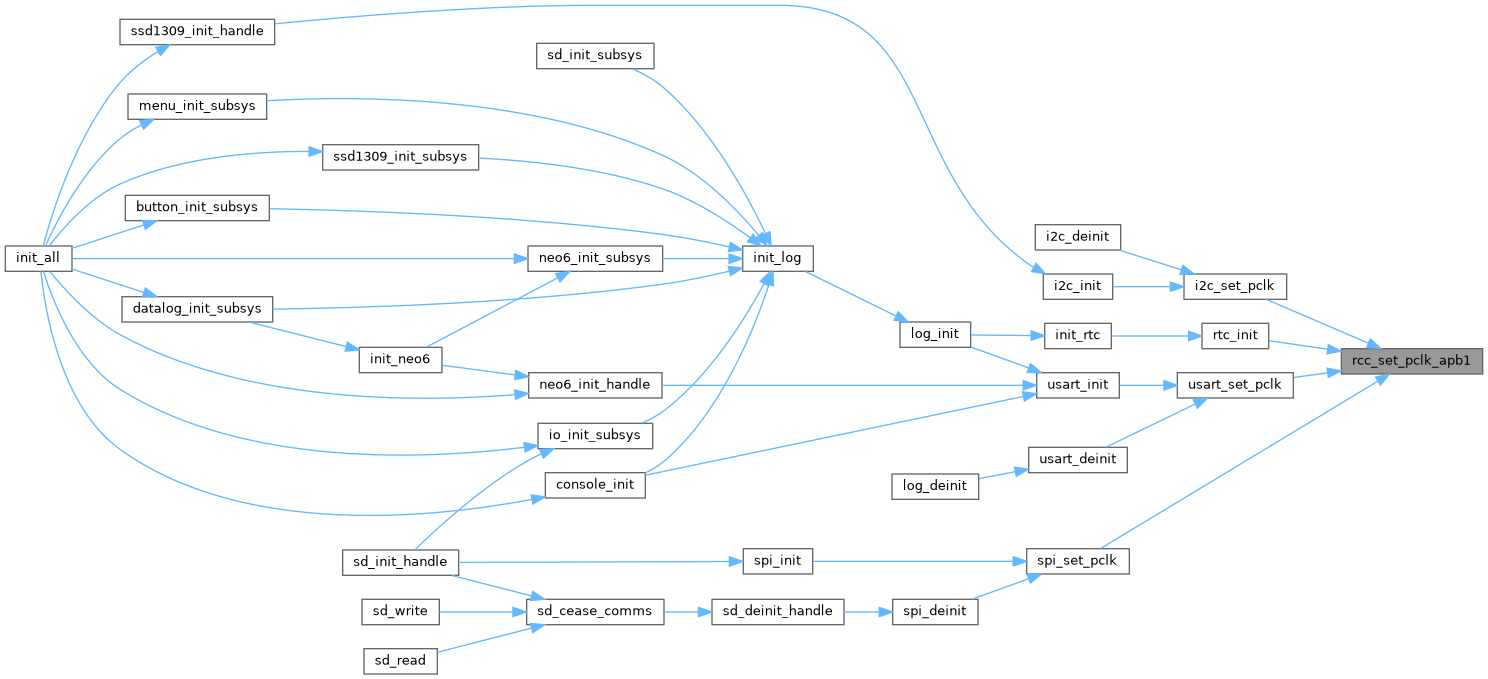

◆ rcc_set_pclk_apb1()

| void rcc_set_pclk_apb1 | ( | RCC_APB1ENR_te | periph_position, |

| EN_STATUS_te | en_status ) |

Enables or disables the peripheral clock for an APB1 peripheral.

- Parameters

-

[in] periph_position Bit position in RCC_APB1ENR for the target peripheral. [in] en_status ENABLE to enable the clock, DISABLE to disable it.

- See also

- rcc_set_pclk_apb1

Definition at line 97 of file stm32f401re_rcc.c.

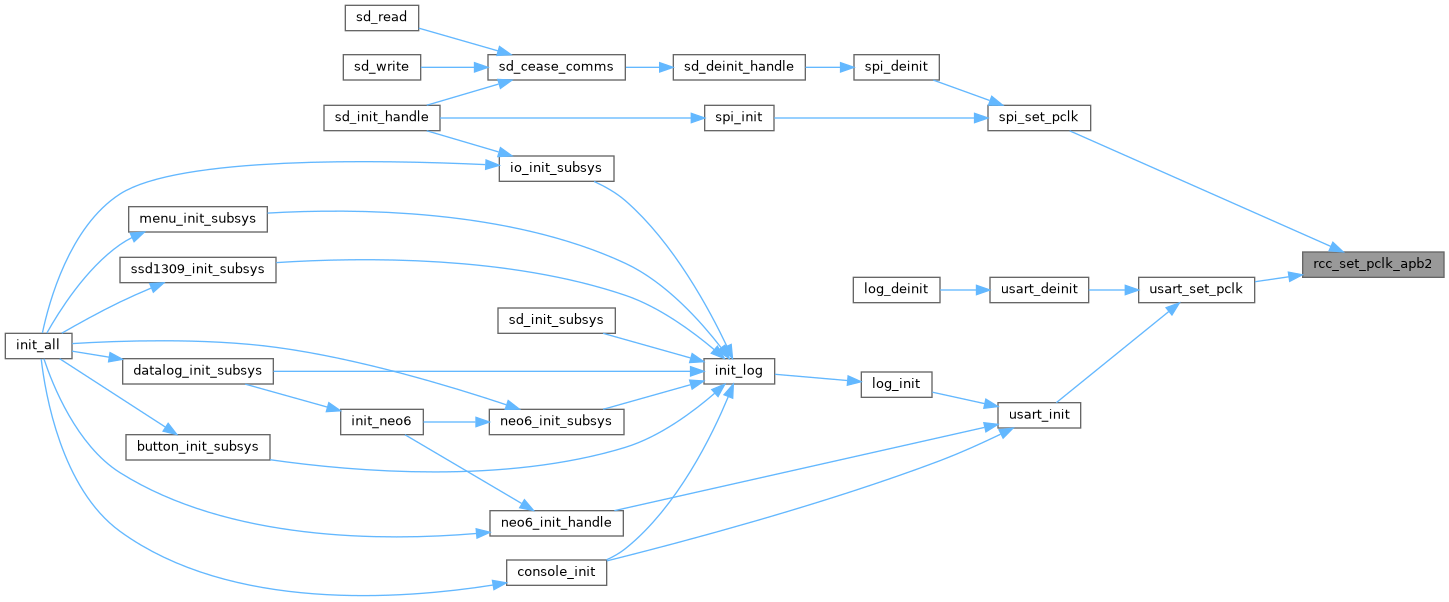

◆ rcc_set_pclk_apb2()

| void rcc_set_pclk_apb2 | ( | RCC_APB2ENR_te | periph_position, |

| EN_STATUS_te | en_status ) |

Enables or disables the peripheral clock for an APB2 peripheral.

- Parameters

-

[in] periph_position Bit position in RCC_APB2ENR for the target peripheral. [in] en_status ENABLE to enable the clock, DISABLE to disable it.

- See also

- rcc_set_pclk_apb2

Definition at line 107 of file stm32f401re_rcc.c.

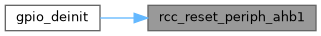

◆ rcc_reset_periph_ahb1()

| void rcc_reset_periph_ahb1 | ( | RCC_AHB1RSTR_te | periph_position | ) |

Resets an AHB1 peripheral via RCC_AHB1RSTR.

Sets the reset bit then clears it, triggering a peripheral reset pulse.

- Parameters

-

[in] periph_position Bit position in RCC_AHB1RSTR for the target peripheral.

- See also

- rcc_reset_periph_ahb1

Definition at line 117 of file stm32f401re_rcc.c.

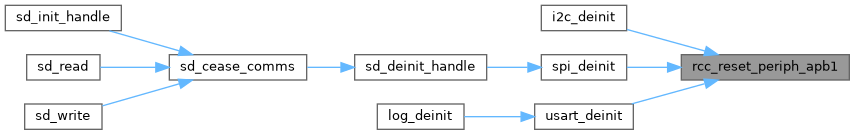

◆ rcc_reset_periph_apb1()

| void rcc_reset_periph_apb1 | ( | RCC_APB1RSTR_te | periph_position | ) |

Resets an APB1 peripheral via RCC_APB1RSTR.

Sets the reset bit then clears it, triggering a peripheral reset pulse.

- Parameters

-

[in] periph_position Bit position in RCC_APB1RSTR for the target peripheral.

- See also

- rcc_reset_periph_apb1

Definition at line 123 of file stm32f401re_rcc.c.

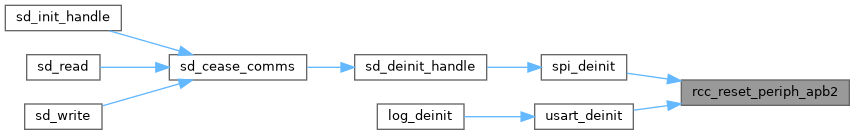

◆ rcc_reset_periph_apb2()

| void rcc_reset_periph_apb2 | ( | RCC_APB2RSTR_te | periph_position | ) |

Resets an APB2 peripheral via RCC_APB2RSTR.

Sets the reset bit then clears it, triggering a peripheral reset pulse.

- Parameters

-

[in] periph_position Bit position in RCC_APB2RSTR for the target peripheral.

- See also

- rcc_reset_periph_apb2

Definition at line 129 of file stm32f401re_rcc.c.

◆ rcc_reset_bkpd()

| void rcc_reset_bkpd | ( | void | ) |

Resets the backup domain (RTC, backup registers, backup SRAM).

Sets then clears the BDRST bit in RCC_BDCR, resetting all backup domain logic including the RTC, backup registers, and backup SRAM controller.

- Note

- This also clears the RTC clock source selection. Re-configure the RTC clock source after calling this function.

Resets the backup domain (RTC, backup registers, backup SRAM).

- See also

- rcc_reset_bkpd

Definition at line 135 of file stm32f401re_rcc.c.