Functions | |

| uint32_t | rcc_get_sysclk (void) |

| Returns the current system clock frequency in Hz. | |

| uint32_t | rcc_get_ahb_clk (void) |

| Returns the current AHB bus clock frequency in Hz. | |

| uint32_t | rcc_get_apb1_clk (void) |

| Returns the current APB1 peripheral bus clock frequency in Hz. | |

| uint32_t | rcc_get_apb2_clk (void) |

| Returns the current APB2 peripheral bus clock frequency in Hz. | |

| void | rcc_set_pclk_ahb1 (RCC_AHB1ENR_te periph_position, EN_STATUS_te en_status) |

| Enables or disables the peripheral clock for an AHB1 peripheral. | |

| void | rcc_set_pclk_apb1 (RCC_APB1ENR_te periph_position, EN_STATUS_te en_status) |

| Enables or disables the peripheral clock for an APB1 peripheral. | |

| void | rcc_set_pclk_apb2 (RCC_APB2ENR_te periph_position, EN_STATUS_te en_status) |

| Enables or disables the peripheral clock for an APB2 peripheral. | |

| void | rcc_reset_periph_ahb1 (RCC_AHB1RSTR_te periph_position) |

| Resets an AHB1 peripheral via RCC_AHB1RSTR. | |

| void | rcc_reset_periph_apb1 (RCC_APB1RSTR_te periph_position) |

| Resets an APB1 peripheral via RCC_APB1RSTR. | |

| void | rcc_reset_periph_apb2 (RCC_APB2RSTR_te periph_position) |

| Resets an APB2 peripheral via RCC_APB2RSTR. | |

| void | rcc_reset_bkpd (void) |

| Resets the backup domain. | |

Detailed Description

Function Documentation

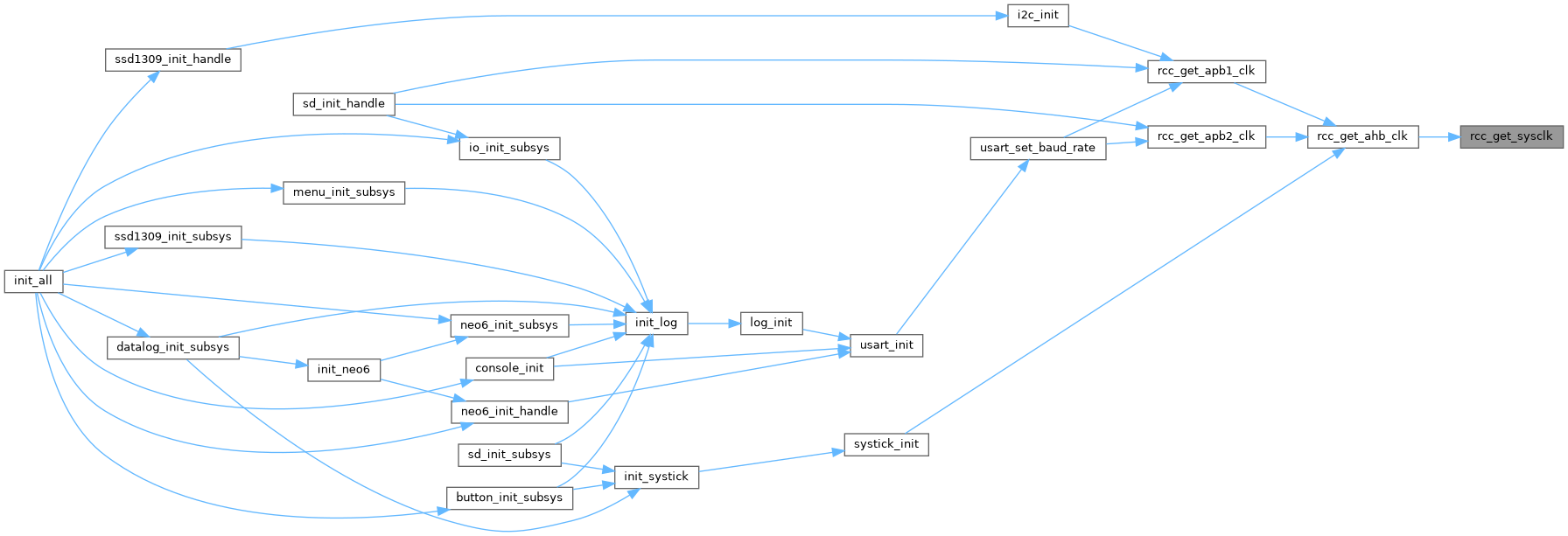

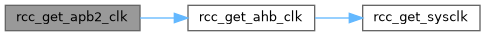

◆ rcc_get_sysclk()

| uint32_t rcc_get_sysclk | ( | void | ) |

Returns the current system clock frequency in Hz.

- See also

- rcc_get_sysclk

Definition at line 21 of file stm32f401re_rcc.c.

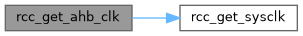

◆ rcc_get_ahb_clk()

| uint32_t rcc_get_ahb_clk | ( | void | ) |

Returns the current AHB bus clock frequency in Hz.

- See also

- rcc_get_ahb_clk

Definition at line 36 of file stm32f401re_rcc.c.

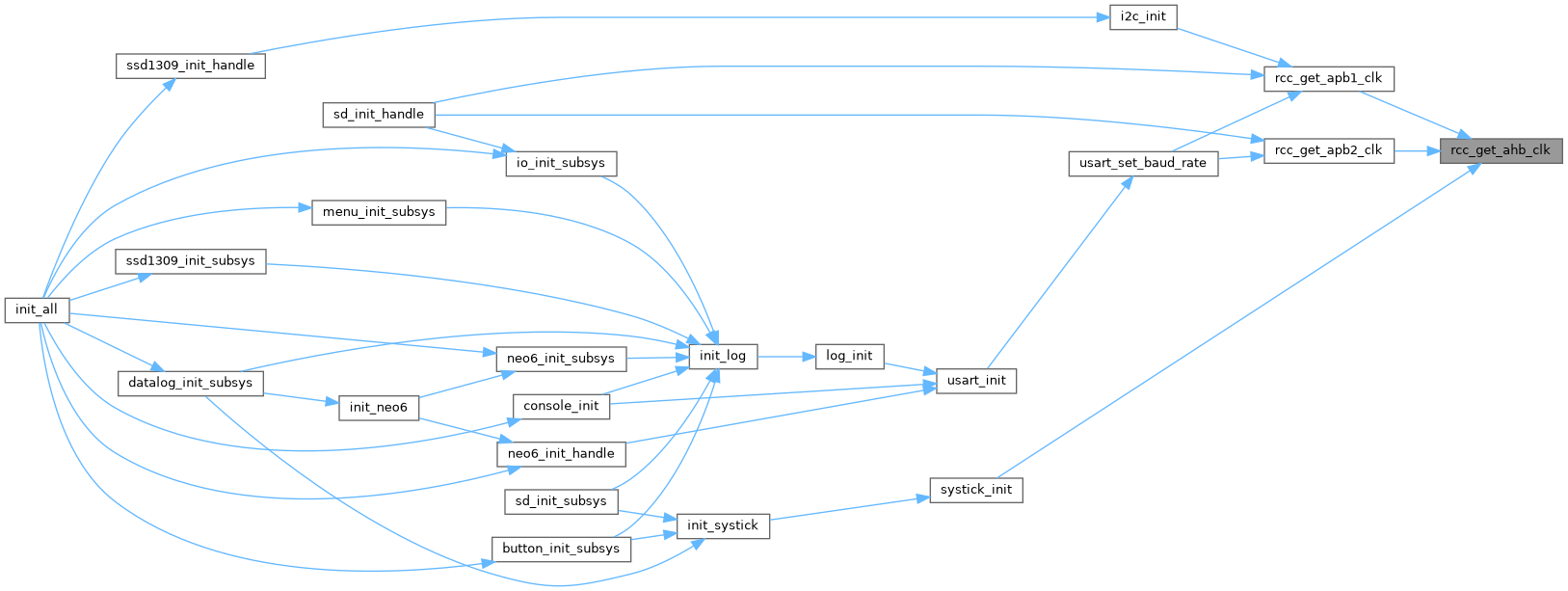

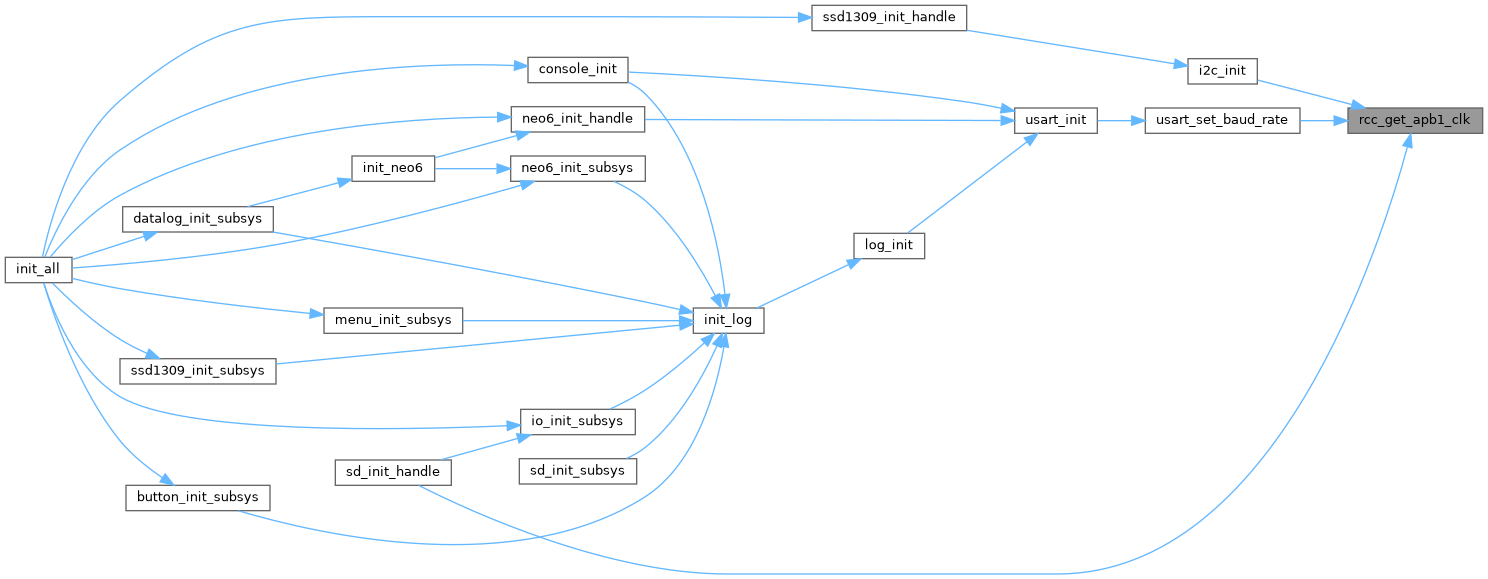

◆ rcc_get_apb1_clk()

| uint32_t rcc_get_apb1_clk | ( | void | ) |

Returns the current APB1 peripheral bus clock frequency in Hz.

Returns the current APB1 (low-speed) peripheral bus clock frequency in Hz.

- See also

- rcc_get_apb1_clk

Definition at line 55 of file stm32f401re_rcc.c.

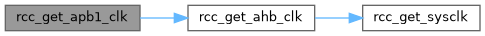

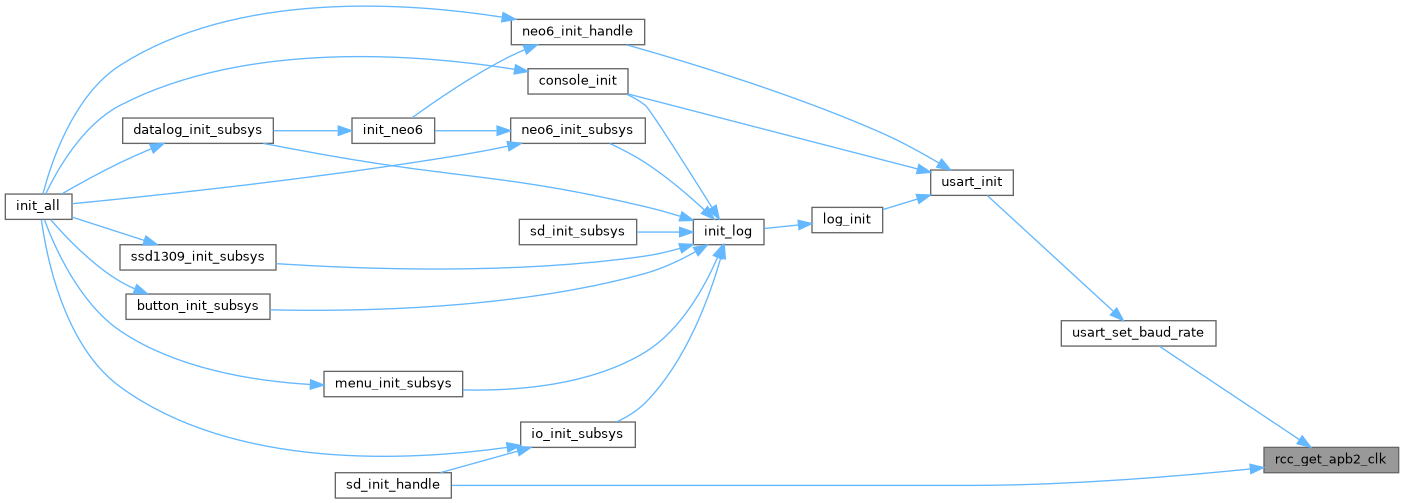

◆ rcc_get_apb2_clk()

| uint32_t rcc_get_apb2_clk | ( | void | ) |

Returns the current APB2 peripheral bus clock frequency in Hz.

Returns the current APB2 (high-speed) peripheral bus clock frequency in Hz.

- See also

- rcc_get_apb2_clk

Definition at line 71 of file stm32f401re_rcc.c.

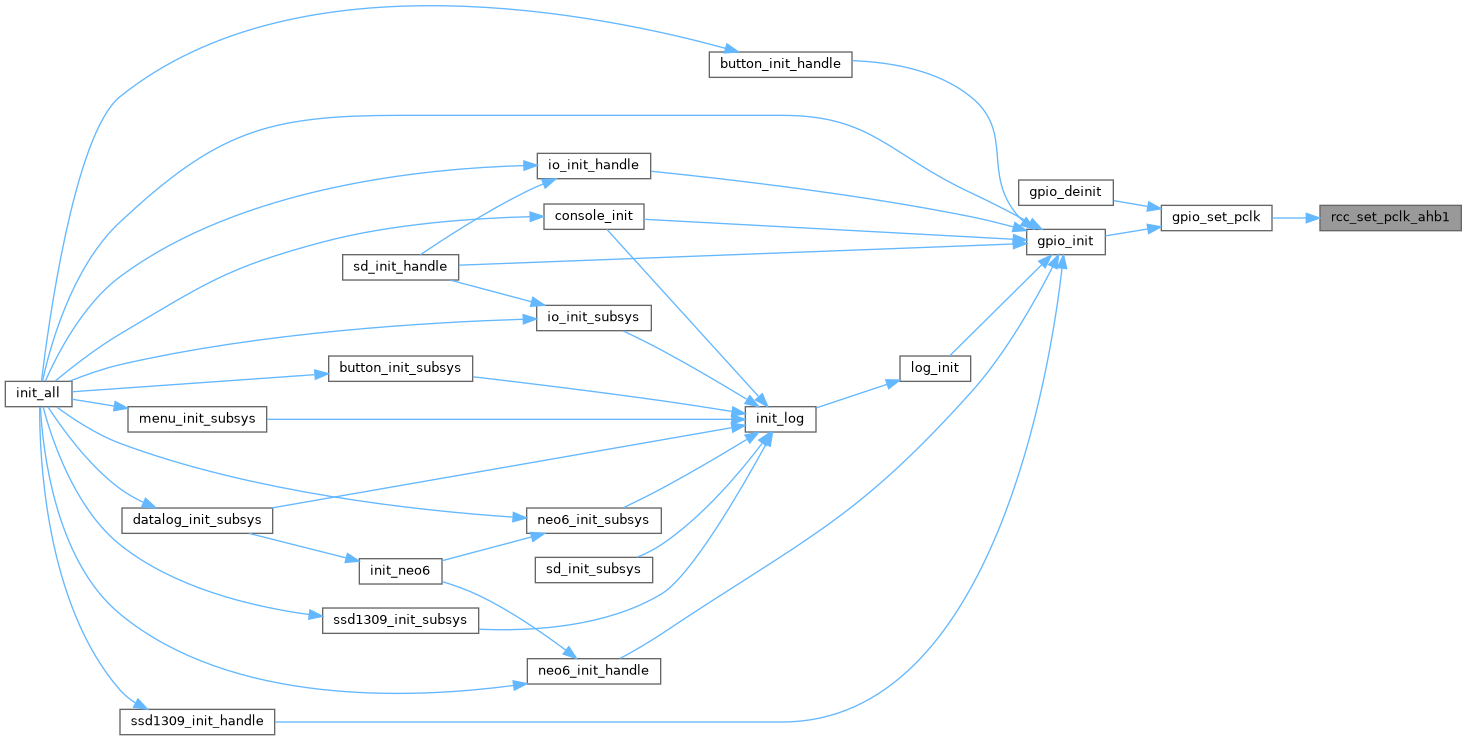

◆ rcc_set_pclk_ahb1()

| void rcc_set_pclk_ahb1 | ( | RCC_AHB1ENR_te | periph_position, |

| EN_STATUS_te | en_status ) |

Enables or disables the peripheral clock for an AHB1 peripheral.

- See also

- rcc_set_pclk_ahb1

Definition at line 87 of file stm32f401re_rcc.c.

◆ rcc_set_pclk_apb1()

| void rcc_set_pclk_apb1 | ( | RCC_APB1ENR_te | periph_position, |

| EN_STATUS_te | en_status ) |

Enables or disables the peripheral clock for an APB1 peripheral.

- See also

- rcc_set_pclk_apb1

Definition at line 97 of file stm32f401re_rcc.c.

◆ rcc_set_pclk_apb2()

| void rcc_set_pclk_apb2 | ( | RCC_APB2ENR_te | periph_position, |

| EN_STATUS_te | en_status ) |

Enables or disables the peripheral clock for an APB2 peripheral.

- See also

- rcc_set_pclk_apb2

Definition at line 107 of file stm32f401re_rcc.c.

◆ rcc_reset_periph_ahb1()

| void rcc_reset_periph_ahb1 | ( | RCC_AHB1RSTR_te | periph_position | ) |

Resets an AHB1 peripheral via RCC_AHB1RSTR.

- See also

- rcc_reset_periph_ahb1

Definition at line 117 of file stm32f401re_rcc.c.

◆ rcc_reset_periph_apb1()

| void rcc_reset_periph_apb1 | ( | RCC_APB1RSTR_te | periph_position | ) |

Resets an APB1 peripheral via RCC_APB1RSTR.

- See also

- rcc_reset_periph_apb1

Definition at line 123 of file stm32f401re_rcc.c.

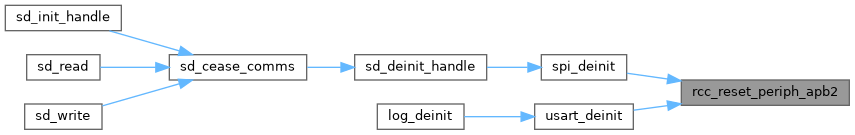

◆ rcc_reset_periph_apb2()

| void rcc_reset_periph_apb2 | ( | RCC_APB2RSTR_te | periph_position | ) |

Resets an APB2 peripheral via RCC_APB2RSTR.

- See also

- rcc_reset_periph_apb2

Definition at line 129 of file stm32f401re_rcc.c.

◆ rcc_reset_bkpd()

| void rcc_reset_bkpd | ( | void | ) |

Resets the backup domain.

Resets the backup domain (RTC, backup registers, backup SRAM).

- See also

- rcc_reset_bkpd

Definition at line 135 of file stm32f401re_rcc.c.