Loading...

Searching...

No Matches

stm32f401re_spi.h File Reference

STM32F401RE SPI driver public API. More...

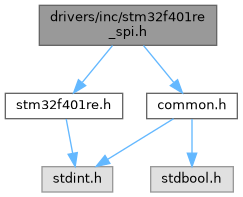

Include dependency graph for stm32f401re_spi.h:

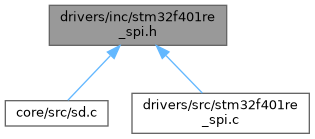

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | SPI_CFG_ts |

| Configuration structure for initializing an SPI peripheral. More... | |

Functions | |

| void | spi_init (SPI_CFG_ts *spi_cfg) |

| Initializes the SPI peripheral with the given configuration. | |

| void | spi_deinit (SPI_REGDEF_ts const *spi_instance) |

| Deinitializes the SPI peripheral and disables its clock. | |

| void | spi_send (SPI_REGDEF_ts *spi_instance, uint8_t *tx_buffer, uint32_t len) |

Blocking SPI transmit. Sends len bytes from tx_buffer. | |

| void | spi_receive (SPI_REGDEF_ts *spi_instance, uint8_t *rx_buffer, uint32_t len) |

Blocking SPI receive. Reads len bytes into rx_buffer. | |

| void | spi_set_pclk_div (SPI_REGDEF_ts *spi_instance, SPI_MASTER_SCLK_SPEED_te pclk_div) |

| Changes the SPI master clock speed divisor at runtime. | |

| void | spi_set_comm (SPI_REGDEF_ts *spi_instance, EN_STATUS_te en_status) |

| Enables or disables the SPI peripheral (SPE bit). | |

Detailed Description

STM32F401RE SPI driver public API.

This module provides a blocking full-duplex SPI driver for the STM32F401RE, supporting master and slave modes, 8-bit and 16-bit data frames, hardware and software slave select, and all four SPI clock modes (CPOL/CPHA).

All transfer functions are blocking — they poll status flags and return only after the transfer completes. Peripheral clock management is handled internally.

The driver separates peripheral configuration from bus enablement:

- spi_init configures the peripheral registers but does not enable it.

- spi_set_comm enables (SPE = 1) or disables (waits for BSY, then SPE = 0) the peripheral, controlling bus ownership.

Typical usage:

- Populate an SPI_CFG_ts and call spi_init

- Call spi_set_comm with ENABLE before the first transfer

- Call spi_send and/or spi_receive

- Call spi_set_comm with DISABLE after the last transfer

- Version

- 0.1

- Date

- 2026-01-30

- Copyright

- Copyright (c) 2026

Definition in file stm32f401re_spi.h.