Configuration structure for initializing an SPI peripheral. More...

#include <stm32f401re_spi.h>

Detailed Description

Configuration structure for initializing an SPI peripheral.

Passed to spi_init. It is recommended to zero-initialize this structure before use. Fields that are irrelevant for the selected mode are ignored:

- master_sclk_speed is only used in SPI_MODE_MASTER.

Definition at line 137 of file stm32f401re_spi.h.

Member Data Documentation

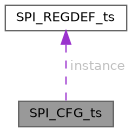

◆ instance

| SPI_REGDEF_ts* SPI_CFG_ts::instance |

Pointer to the SPI peripheral instance (SPI1–SPI4).

Definition at line 139 of file stm32f401re_spi.h.

◆ mode

| SPI_MODE_te SPI_CFG_ts::mode |

Operating mode: master or slave.

Definition at line 142 of file stm32f401re_spi.h.

◆ data_frame_format

| SPI_DATA_FRAME_FORMAT_te SPI_CFG_ts::data_frame_format |

Data frame size: 8-bit or 16-bit.

Definition at line 145 of file stm32f401re_spi.h.

◆ clock_polarity

| SPI_CLOCK_POLARITY_te SPI_CFG_ts::clock_polarity |

SCLK idle polarity (CPOL).

Definition at line 148 of file stm32f401re_spi.h.

◆ clock_phase

| SPI_CLOCK_PHASE_te SPI_CFG_ts::clock_phase |

Data capture edge (CPHA).

Definition at line 151 of file stm32f401re_spi.h.

◆ bit_first

| SPI_BIT_FIRST_te SPI_CFG_ts::bit_first |

Bit transmission order (MSB or LSB first).

Definition at line 154 of file stm32f401re_spi.h.

◆ slave_select_mode

| SPI_SLAVE_SELECT_MODE_te SPI_CFG_ts::slave_select_mode |

NSS (slave select) management mode: hardware or software.

Definition at line 157 of file stm32f401re_spi.h.

◆ master_sclk_speed

| SPI_MASTER_SCLK_SPEED_te SPI_CFG_ts::master_sclk_speed |

Master SCK speed as a PCLK divisor. Only used in master mode.

Definition at line 160 of file stm32f401re_spi.h.

The documentation for this struct was generated from the following file:

- drivers/inc/stm32f401re_spi.h