Public functions to interact with the SPI peripheral. More...

Functions | |

| void | spi_init (SPI_CFG_ts *spi_cfg) |

| Initializes the SPI peripheral with the given configuration. | |

| void | spi_deinit (SPI_REGDEF_ts const *spi_instance) |

| Deinitializes the SPI peripheral and disables its clock. | |

| void | spi_send (SPI_REGDEF_ts *spi_instance, uint8_t *tx_buffer, uint32_t len) |

Blocking SPI transmit. Sends len bytes from tx_buffer. | |

| void | spi_receive (SPI_REGDEF_ts *spi_instance, uint8_t *rx_buffer, uint32_t len) |

Blocking SPI receive. Reads len bytes into rx_buffer. | |

| void | spi_set_pclk_div (SPI_REGDEF_ts *spi_instance, SPI_MASTER_SCLK_SPEED_te pclk_div) |

| Changes the SPI master clock speed divisor at runtime. | |

| void | spi_set_comm (SPI_REGDEF_ts *spi_instance, EN_STATUS_te en_status) |

| Enables or disables the SPI peripheral (SPE bit). | |

Detailed Description

Public functions to interact with the SPI peripheral.

Function Documentation

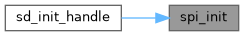

◆ spi_init()

| void spi_init | ( | SPI_CFG_ts * | spi_cfg | ) |

Initializes the SPI peripheral with the given configuration.

Enables the peripheral clock and configures data frame format, clock polarity, clock phase, bit order, slave select mode, master/slave mode, and (in master mode) the SCK speed. Does not enable the peripheral for communication; call spi_set_comm with ENABLE to do so.

Default values if fields are zero-initialized:

- Mode: slave

- Data frame: 8-bit

- Clock polarity: idle low (CPOL = 0)

- Clock phase: first transition (CPHA = 0)

- Bit order: MSB first

- Slave select: hardware

- Master speed: PCLK / 2

- Parameters

-

[in] spi_cfg Pointer to the SPI configuration structure.

- Note

- It is recommended to zero-initialize SPI_CFG_ts before use.

- See also

- spi_init

Definition at line 24 of file stm32f401re_spi.c.

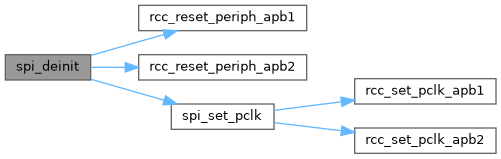

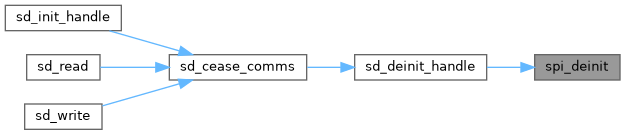

◆ spi_deinit()

| void spi_deinit | ( | SPI_REGDEF_ts const * | instance | ) |

Deinitializes the SPI peripheral and disables its clock.

Triggers an RCC peripheral reset for the given instance and then disables the peripheral clock.

- Parameters

-

[in] spi_instance Pointer to the SPI instance to deinitialize.

- See also

- spi_deinit

Definition at line 72 of file stm32f401re_spi.c.

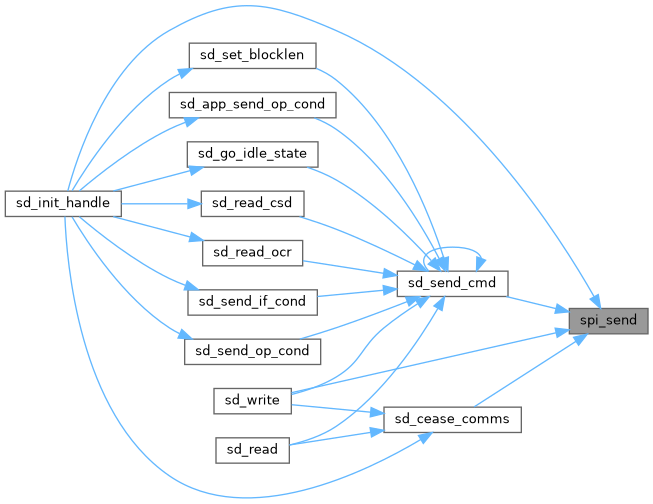

◆ spi_send()

| void spi_send | ( | SPI_REGDEF_ts * | instance, |

| uint8_t * | tx_buffer, | ||

| uint32_t | len ) |

Blocking SPI transmit. Sends len bytes from tx_buffer.

Transmits data one frame at a time, polling TXE before each write and RXNE after each write to drain the receive FIFO (required in full-duplex mode to prevent overrun). Supports both 8-bit and 16-bit frame formats.

- Parameters

-

[in] spi_instance Pointer to the SPI peripheral instance. [in] tx_buffer Pointer to the transmit data buffer. [in] len Number of bytes to transmit. Must be even for 16-bit frames.

- Note

- The peripheral must be enabled via spi_set_comm before calling this function.

Blocking SPI transmit. Sends len bytes from tx_buffer.

- See also

- spi_send

Definition at line 90 of file stm32f401re_spi.c.

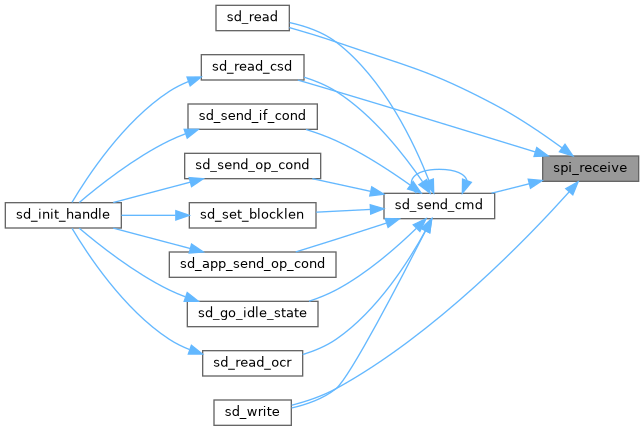

◆ spi_receive()

| void spi_receive | ( | SPI_REGDEF_ts * | instance, |

| uint8_t * | rx_buffer, | ||

| uint32_t | len ) |

Blocking SPI receive. Reads len bytes into rx_buffer.

Receives data by transmitting dummy bytes (0xFF) to generate the SCK clock signal, then reads the received byte from the data register. Supports both 8-bit and 16-bit frame formats.

- Parameters

-

[in] spi_instance Pointer to the SPI peripheral instance. [out] rx_buffer Pointer to the receive data buffer. [in] len Number of bytes to receive. Must be even for 16-bit frames.

- Note

- The peripheral must be enabled via spi_set_comm before calling this function.

Blocking SPI receive. Reads len bytes into rx_buffer.

- See also

- spi_receive

Definition at line 115 of file stm32f401re_spi.c.

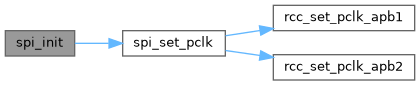

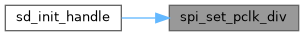

◆ spi_set_pclk_div()

| void spi_set_pclk_div | ( | SPI_REGDEF_ts * | spi_instance, |

| SPI_MASTER_SCLK_SPEED_te | pclk_div ) |

Changes the SPI master clock speed divisor at runtime.

Updates the BR field in SPI_CR1 without a full re-initialization. Used by the SD card driver to ramp the SCK from the slow initialization speed (100–400 kHz) to the maximum speed after card initialization.

- Parameters

-

[in] spi_instance Pointer to the SPI peripheral instance. [in] pclk_div The new clock divisor to apply.

- Note

- The peripheral should be disabled (SPE = 0) before changing BR. In practice this is called between transactions so the peripheral is idle, but be cautious if calling mid-transaction.

- See also

- spi_set_pclk_div

Definition at line 143 of file stm32f401re_spi.c.

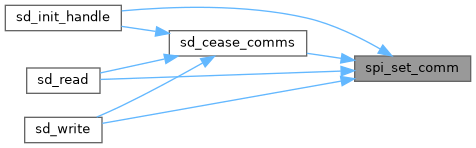

◆ spi_set_comm()

| void spi_set_comm | ( | SPI_REGDEF_ts * | instance, |

| EN_STATUS_te | en_status ) |

Enables or disables the SPI peripheral (SPE bit).

- ENABLE: sets SPE, activating the peripheral for communication. Must be called before the first spi_send or spi_receive.

- DISABLE: waits for the BSY flag to clear (transfer complete), then clears SPE. Must be called after the last transfer.

- Parameters

-

[in] spi_instance Pointer to the SPI peripheral instance. [in] en_status ENABLE to activate, DISABLE to deactivate.

Enables or disables the SPI peripheral (SPE bit).

- See also

- spi_set_comm

Definition at line 149 of file stm32f401re_spi.c.