Loading...

Searching...

No Matches

stm32f401re_rcc.h File Reference

STM32F401RE RCC driver public API. More...

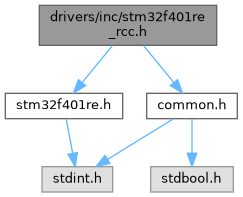

Include dependency graph for stm32f401re_rcc.h:

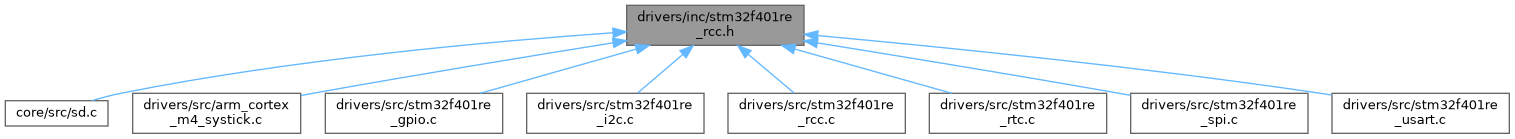

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Functions | |

| uint32_t | rcc_get_sysclk (void) |

| Returns the current system clock frequency in Hz. | |

| uint32_t | rcc_get_ahb_clk (void) |

| Returns the current AHB bus clock frequency in Hz. | |

| uint32_t | rcc_get_apb1_clk (void) |

| Returns the current APB1 (low-speed) peripheral bus clock frequency in Hz. | |

| uint32_t | rcc_get_apb2_clk (void) |

| Returns the current APB2 (high-speed) peripheral bus clock frequency in Hz. | |

| void | rcc_set_pclk_ahb1 (RCC_AHB1ENR_te periph_position, EN_STATUS_te en_status) |

| Enables or disables the peripheral clock for an AHB1 peripheral. | |

| void | rcc_set_pclk_apb1 (RCC_APB1ENR_te periph_position, EN_STATUS_te en_status) |

| Enables or disables the peripheral clock for an APB1 peripheral. | |

| void | rcc_set_pclk_apb2 (RCC_APB2ENR_te periph_position, EN_STATUS_te en_status) |

| Enables or disables the peripheral clock for an APB2 peripheral. | |

| void | rcc_reset_periph_ahb1 (RCC_AHB1RSTR_te periph_position) |

| Resets an AHB1 peripheral via RCC_AHB1RSTR. | |

| void | rcc_reset_periph_apb1 (RCC_APB1RSTR_te periph_position) |

| Resets an APB1 peripheral via RCC_APB1RSTR. | |

| void | rcc_reset_periph_apb2 (RCC_APB2RSTR_te periph_position) |

| Resets an APB2 peripheral via RCC_APB2RSTR. | |

| void | rcc_reset_bkpd (void) |

| Resets the backup domain (RTC, backup registers, backup SRAM). | |

Detailed Description

STM32F401RE RCC driver public API.

This module provides a software interface to the STM32F401RE Reset and Clock Control (RCC) peripheral, covering:

- Reading the current system, AHB, APB1, and APB2 clock frequencies

- Enabling and disabling peripheral clocks on AHB1, APB1, and APB2

- Resetting peripherals on AHB1, APB1, and APB2 via the reset registers

- Resetting the backup domain

Clock frequency functions read the current CFGR prescaler fields at call time, so they always reflect the live clock tree configuration.

- Note

- PLL as system clock source is not yet implemented. Only HSI (16 MHz) and HSE (8 MHz) are currently supported by rcc_get_sysclk.

- Version

- 0.1

- Date

- 2026-01-23

- Copyright

- Copyright (c) 2026

Definition in file stm32f401re_rcc.h.