Functions | |

| void | i2c_init (I2C_CFG_ts *i2c_cfg) |

| Initializes the I2C peripheral with the given configuration. | |

| void | i2c_deinit (I2C_REGDEF_ts const *i2c_instance) |

| Deinitializes the I2C peripheral and disables its clock. | |

| void | i2c_master_send (I2C_REGDEF_ts *i2c_instance, uint8_t slave_addr, uint8_t *tx_buffer, uint32_t len) |

| Blocking I2C master transmit. | |

| void | i2c_master_send_continue (I2C_REGDEF_ts *i2c_instance, uint8_t *tx_buffer, uint32_t len) |

| Continues a transmission without a new START or address phase. | |

| void | i2c_master_receive (I2C_REGDEF_ts *i2c_instance, uint8_t slave_addr, uint8_t *rx_buffer, uint32_t len) |

| Blocking I2C master receive. | |

| void | i2c_master_set_comm (I2C_REGDEF_ts *i2c_instance, EN_STATUS_te en_status) |

| Enables or disables the I2C peripheral and controls bus ownership. | |

| void | i2c_get_name (I2C_REGDEF_ts const *i2c_instance, char *name) |

| Returns the name string of an I2C peripheral instance. | |

Detailed Description

Function Documentation

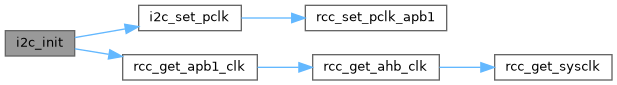

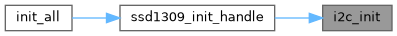

◆ i2c_init()

| void i2c_init | ( | I2C_CFG_ts * | i2c_cfg | ) |

Initializes the I2C peripheral with the given configuration.

- See also

- i2c_init

Definition at line 24 of file stm32f401re_i2c.c.

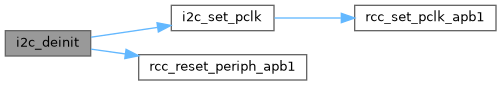

◆ i2c_deinit()

| void i2c_deinit | ( | I2C_REGDEF_ts const * | i2c_instance | ) |

Deinitializes the I2C peripheral and disables its clock.

- See also

- i2c_deinit

Definition at line 77 of file stm32f401re_i2c.c.

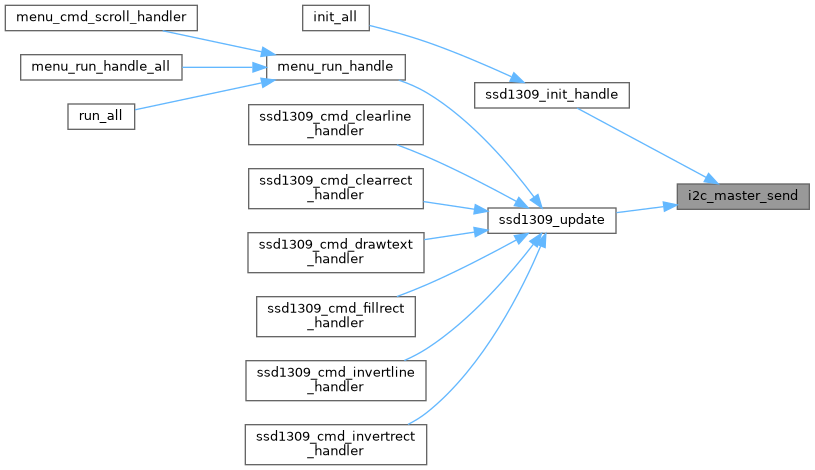

◆ i2c_master_send()

| void i2c_master_send | ( | I2C_REGDEF_ts * | i2c_instance, |

| uint8_t | slave_addr, | ||

| uint8_t * | tx_buffer, | ||

| uint32_t | len ) |

Blocking I2C master transmit.

Blocking I2C master transmit. Sends a start condition, address, and data.

- See also

- i2c_master_send

Definition at line 92 of file stm32f401re_i2c.c.

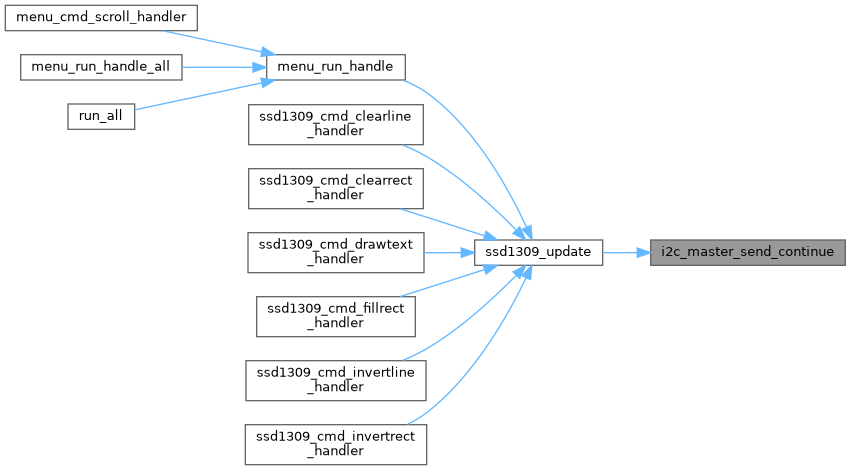

◆ i2c_master_send_continue()

| void i2c_master_send_continue | ( | I2C_REGDEF_ts * | i2c_instance, |

| uint8_t * | tx_buffer, | ||

| uint32_t | len ) |

Continues a transmission without a new START or address phase.

Continues a transmission started by i2c_master_send without a new START or address phase.

- See also

- i2c_master_send_continue

Definition at line 125 of file stm32f401re_i2c.c.

◆ i2c_master_receive()

| void i2c_master_receive | ( | I2C_REGDEF_ts * | i2c_instance, |

| uint8_t | slave_addr, | ||

| uint8_t * | rx_buffer, | ||

| uint32_t | len ) |

Blocking I2C master receive.

Blocking I2C master receive. Sends a start condition, address, and reads data.

- See also

- i2c_master_receive

Definition at line 143 of file stm32f401re_i2c.c.

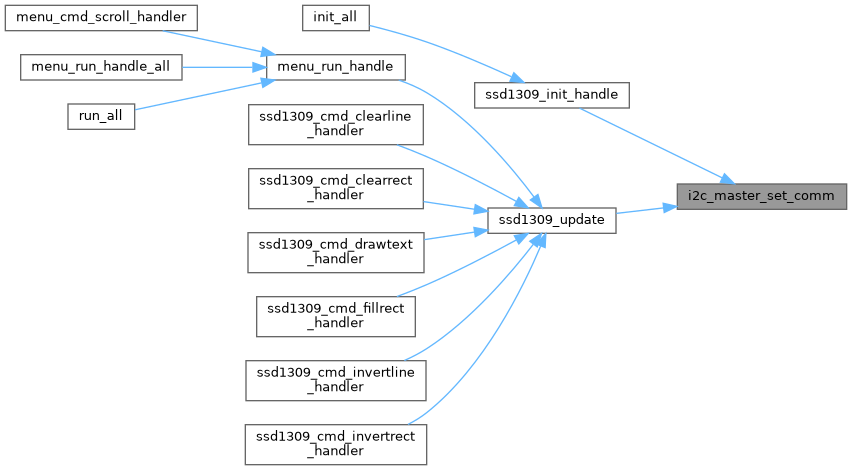

◆ i2c_master_set_comm()

| void i2c_master_set_comm | ( | I2C_REGDEF_ts * | i2c_instance, |

| EN_STATUS_te | en_status ) |

Enables or disables the I2C peripheral and controls bus ownership.

- See also

- i2c_master_set_comm

Definition at line 200 of file stm32f401re_i2c.c.

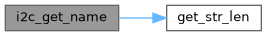

◆ i2c_get_name()

| void i2c_get_name | ( | I2C_REGDEF_ts const * | i2c_instance, |

| char * | name ) |

Returns the name string of an I2C peripheral instance.

Returns the name string of an I2C peripheral instance (e.g. "I2C1").

- See also

- i2c_get_name

Definition at line 215 of file stm32f401re_i2c.c.