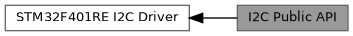

Public functions to interact with the I2C peripheral. More...

Functions | |

| void | i2c_init (I2C_CFG_ts *i2c_cfg) |

| Initializes the I2C peripheral with the given configuration. | |

| void | i2c_deinit (I2C_REGDEF_ts const *i2c_instance) |

| Deinitializes the I2C peripheral and disables its clock. | |

| void | i2c_master_send (I2C_REGDEF_ts *i2c_instance, uint8_t slave_addr, uint8_t *tx_buffer, uint32_t len) |

| Blocking I2C master transmit. Sends a start condition, address, and data. | |

| void | i2c_master_send_continue (I2C_REGDEF_ts *i2c_instance, uint8_t *tx_buffer, uint32_t len) |

| Continues a transmission started by i2c_master_send without a new START or address phase. | |

| void | i2c_master_receive (I2C_REGDEF_ts *i2c_instance, uint8_t slave_addr, uint8_t *rx_buffer, uint32_t len) |

| Blocking I2C master receive. Sends a start condition, address, and reads data. | |

| void | i2c_master_set_comm (I2C_REGDEF_ts *i2c_instance, EN_STATUS_te en_status) |

| Enables or disables the I2C peripheral and controls bus ownership. | |

| void | i2c_get_name (I2C_REGDEF_ts const *i2c_instance, char *name) |

| Returns the name string of an I2C peripheral instance (e.g. "I2C1"). | |

Detailed Description

Public functions to interact with the I2C peripheral.

Function Documentation

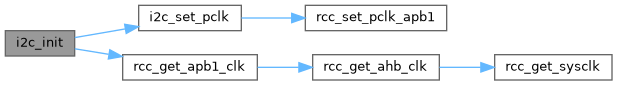

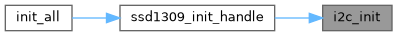

◆ i2c_init()

| void i2c_init | ( | I2C_CFG_ts * | i2c_cfg | ) |

Initializes the I2C peripheral with the given configuration.

Enables the peripheral clock, configures clock stretching, own address, APB1 frequency, CCR, and TRISE. Does not enable the peripheral for communication; call i2c_master_set_comm with ENABLE to do so.

Default values if fields are zero-initialized:

- Clock stretching: enabled

- Own address: 0

- Speed: 100 kHz

- Parameters

-

[in] i2c_cfg Pointer to the I2C configuration structure.

- Note

- It is recommended to zero-initialize I2C_CFG_ts before use to avoid unintended behaviour from uninitialised fields.

- See also

- i2c_init

Definition at line 24 of file stm32f401re_i2c.c.

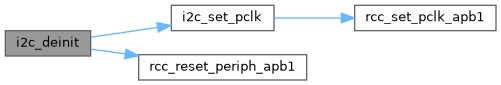

◆ i2c_deinit()

| void i2c_deinit | ( | I2C_REGDEF_ts const * | i2c_instance | ) |

Deinitializes the I2C peripheral and disables its clock.

Triggers an RCC peripheral reset for the given instance and then disables the peripheral clock.

- Parameters

-

[in] i2c_instance Pointer to the I2C instance to deinitialize.

- See also

- i2c_deinit

Definition at line 77 of file stm32f401re_i2c.c.

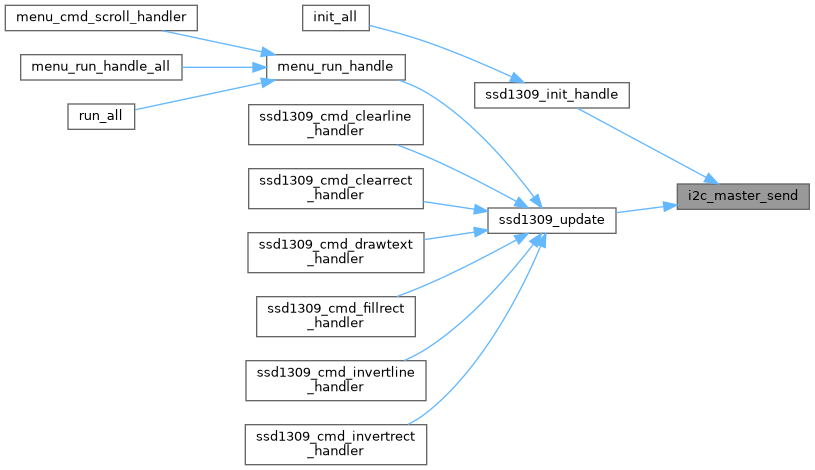

◆ i2c_master_send()

| void i2c_master_send | ( | I2C_REGDEF_ts * | i2c_instance, |

| uint8_t | slave_addr, | ||

| uint8_t * | tx_buffer, | ||

| uint32_t | len ) |

Blocking I2C master transmit. Sends a start condition, address, and data.

Generates a START condition, sends the 7-bit slave address with the write bit, then transmits len bytes from tx_buffer. Waits for BTF (byte transfer finished) after the last byte before returning. Does not generate a STOP condition — call i2c_master_set_comm with DISABLE afterwards to release the bus.

- Parameters

-

[in] i2c_instance Pointer to the I2C peripheral instance. [in] slave_addr 7-bit slave address (right-aligned, without the R/W bit). [in] tx_buffer Pointer to the data buffer to transmit. [in] len Number of bytes to transmit.

- Note

- The peripheral must be enabled via i2c_master_set_comm before calling this function.

Blocking I2C master transmit. Sends a start condition, address, and data.

- See also

- i2c_master_send

Definition at line 92 of file stm32f401re_i2c.c.

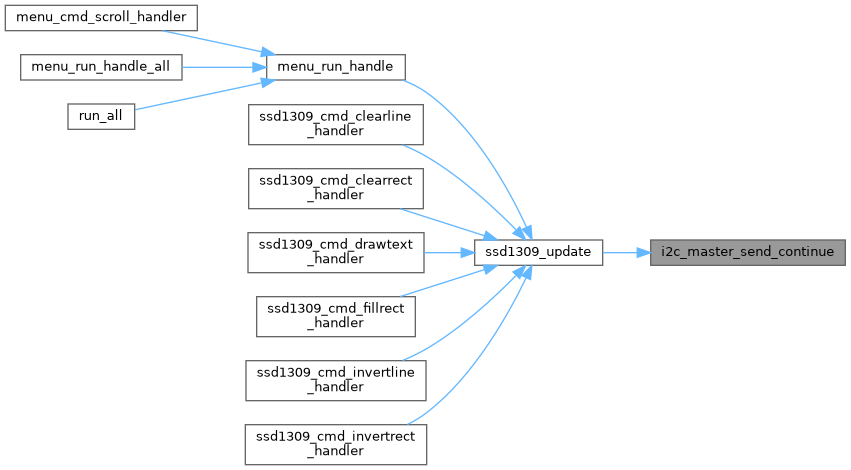

◆ i2c_master_send_continue()

| void i2c_master_send_continue | ( | I2C_REGDEF_ts * | i2c_instance, |

| uint8_t * | tx_buffer, | ||

| uint32_t | len ) |

Continues a transmission started by i2c_master_send without a new START or address phase.

Transmits len additional bytes into an already-open I2C transaction. Useful for sending a command byte followed by a payload in a single bus transaction (e.g. SSD1309 framebuffer transfer).

- Parameters

-

[in] i2c_instance Pointer to the I2C peripheral instance. [in] tx_buffer Pointer to the additional data buffer to transmit. [in] len Number of bytes to transmit.

Continues a transmission started by i2c_master_send without a new START or address phase.

- See also

- i2c_master_send_continue

Definition at line 125 of file stm32f401re_i2c.c.

◆ i2c_master_receive()

| void i2c_master_receive | ( | I2C_REGDEF_ts * | i2c_instance, |

| uint8_t | slave_addr, | ||

| uint8_t * | rx_buffer, | ||

| uint32_t | len ) |

Blocking I2C master receive. Sends a start condition, address, and reads data.

Generates a START condition, sends the 7-bit slave address with the read bit, then receives len bytes into rx_buffer. ACK/NACK is managed automatically: NACK is sent before the last byte to signal end of reception, then ACK is re-enabled before returning.

- Parameters

-

[in] i2c_instance Pointer to the I2C peripheral instance. [in] slave_addr 7-bit slave address (right-aligned, without the R/W bit). [out] rx_buffer Pointer to the buffer that will receive the data. [in] len Number of bytes to receive.

- Note

- The peripheral must be enabled via i2c_master_set_comm before calling this function.

Blocking I2C master receive. Sends a start condition, address, and reads data.

- See also

- i2c_master_receive

Definition at line 143 of file stm32f401re_i2c.c.

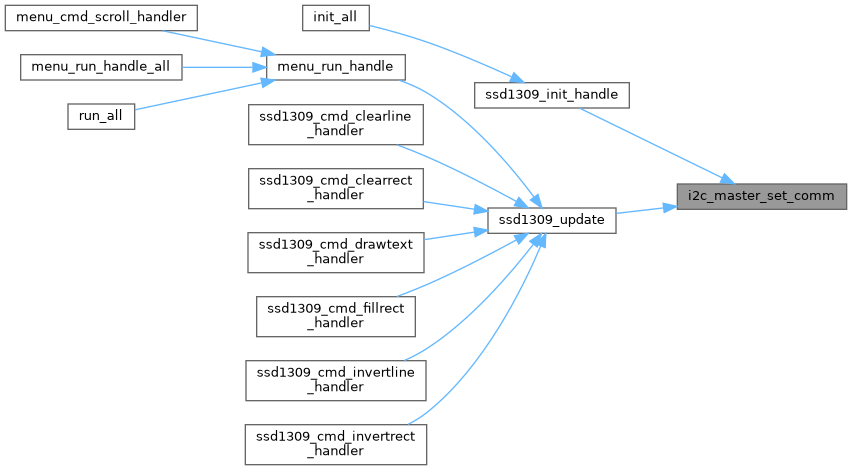

◆ i2c_master_set_comm()

| void i2c_master_set_comm | ( | I2C_REGDEF_ts * | i2c_instance, |

| EN_STATUS_te | en_status ) |

Enables or disables the I2C peripheral and controls bus ownership.

- ENABLE: sets the PE bit, enabling the peripheral, and enables ACK generation. Must be called before any transfer function.

- DISABLE: generates a STOP condition, waits for the bus to become idle (BUSY = 0), then clears PE to release the bus. Must be called after each complete transaction.

Between ENABLE and DISABLE calls the bus is held and cannot be taken by another master.

- Parameters

-

[in] i2c_instance Pointer to the I2C peripheral instance. [in] en_status ENABLE to take the bus, DISABLE to release it.

- See also

- i2c_master_set_comm

Definition at line 200 of file stm32f401re_i2c.c.

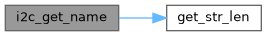

◆ i2c_get_name()

| void i2c_get_name | ( | I2C_REGDEF_ts const * | i2c_instance, |

| char * | name ) |

Returns the name string of an I2C peripheral instance (e.g. "I2C1").

Writes a null-terminated string of the form "I2Cx" into name. The caller must ensure name points to a buffer of at least I2C_NAME_LEN + 1 bytes.

- Parameters

-

[in] i2c_instance Pointer to the I2C peripheral instance. [out] name Pointer to the destination buffer.

Returns the name string of an I2C peripheral instance (e.g. "I2C1").

- See also

- i2c_get_name

Definition at line 215 of file stm32f401re_i2c.c.